- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373913 > AD7679ACP (ANALOG DEVICES INC) 18-Bit, 2.5 LSB INL, 570 kSPS SAR ADC PDF資料下載

參數(shù)資料

| 型號: | AD7679ACP |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 18-Bit, 2.5 LSB INL, 570 kSPS SAR ADC |

| 中文描述: | 1-CH 18-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, QCC48 |

| 封裝: | MO-220-VKKD-2, LFCSP-48 |

| 文件頁數(shù): | 21/28頁 |

| 文件大小: | 1186K |

| 代理商: | AD7679ACP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

AD7679

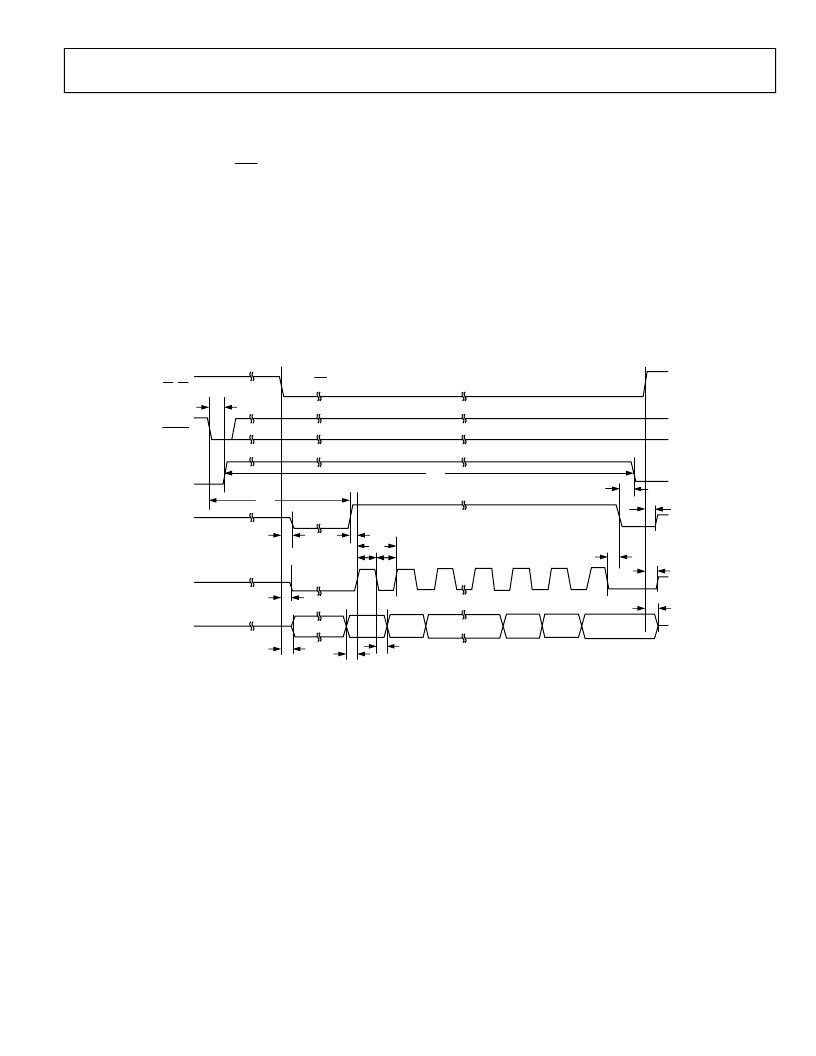

MASTER SERIAL INTERFACE

Internal Clock

The AD7679 is configured to generate and provide the serial

data clock SCLK when the EXT/INT pin is held low. The

AD7679 also generates a SYNC signal to indicate to the host

when the serial data is valid. The serial clock SCLK and the

SYNC signal can be inverted if desired. Depending on the

RDC/SDIN input, the data can be read after each conversion or

during the following conversion. Figure 38 and Figure 39 show

the detailed timing diagrams of these two modes.

In Read during Conversion mode, the serial clock and data

toggle at appropriate instants, minimizing potential feedthrough

between digital activity and critical conversion decisions.

In Read after Conversion mode, it should be noted that unlike

in other modes, the BUSY signal returns low after the 18 data

bits are pulsed out and not at the end of the conversion phase,

which results in a longer BUSY width.

To accommodate slow digital hosts, the serial clock can be

slowed down by using DIVSCLK.

Usually, because the AD7679 is used with a fast throughput, the

mode master read during conversion is the most recommended

serial mode.

t

3

BUSY

CS, RD

CNVST

SYNC

SCLK

SDOUT

1

2

3

16

17

18

D17

D16

D2

D1

D0

X

EXT/INT = 0

RDC/SDIN = 0

INVSCLK = INVSYNC = 0

t

14

t

20

t

15

t

16

t

22

t

23

t

29

t

28

t

18

t

19

t

21

t

30

t

25

t

24

t

26

t

27

03085-0-040

Figure 38. Master Serial Data Timing for Reading (Read after Convert)

Rev. 0 | Page 21 of 28

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7679ACPRL | 18-Bit, 2.5 LSB INL, 570 kSPS SAR ADC |

| AD7679AST | 18-Bit, 2.5 LSB INL, 570 kSPS SAR ADC |

| AD7679ASTRL | 18-Bit, 2.5 LSB INL, 570 kSPS SAR ADC |

| AD7675 | 16-Bit, 100 kSPS, Differential ADC |

| AD7675AST | 16-Bit, 100 kSPS, Differential ADC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7679ACPRL | 制造商:Analog Devices 功能描述:ADC Single SAR 570ksps 18-bit Parallel/Serial 48-Pin LFCSP EP T/R 制造商:Analog Devices 功能描述:ADC SGL SAR 570KSPS 18BIT PARALLEL/SERL 48LFCSP EP - Tape and Reel 制造商:Rochester Electronics LLC 功能描述:18-BIT,100KSPSSARADC - Tape and Reel |

| AD7679ACPZ | 功能描述:IC ADC 18BIT SAR W/BUFF 48LFCSP RoHS:是 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:PulSAR® 標(biāo)準(zhǔn)包裝:1 系列:- 位數(shù):14 采樣率(每秒):83k 數(shù)據(jù)接口:串行,并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應(yīng)商設(shè)備封裝:28-PDIP 包裝:管件 輸入數(shù)目和類型:1 個(gè)單端,雙極 |

| AD7679ACPZRL | 功能描述:IC ADC 18BIT SAR W/BUFF 48LFCSP RoHS:是 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:PulSAR® 標(biāo)準(zhǔn)包裝:1 系列:- 位數(shù):14 采樣率(每秒):83k 數(shù)據(jù)接口:串行,并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應(yīng)商設(shè)備封裝:28-PDIP 包裝:管件 輸入數(shù)目和類型:1 個(gè)單端,雙極 |

| AD7679AST | 制造商:Analog Devices 功能描述:ADC Single SAR 570ksps 18-bit Parallel/Serial 48-Pin LQFP 制造商:Analog Devices 功能描述:18BIT SAR ADC SMD 7679 LQFP48 |

| AD7679ASTRL | 制造商:Analog Devices 功能描述:ADC Single SAR 570ksps 18-bit Parallel/Serial 48-Pin LQFP T/R 制造商:Analog Devices 功能描述:ADC SGL SAR 570KSPS 18BIT PARALLEL/SERL 48LQFP - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。