- 您現在的位置:買賣IC網 > PDF目錄373913 > AD7679ACP (ANALOG DEVICES INC) 18-Bit, 2.5 LSB INL, 570 kSPS SAR ADC PDF資料下載

參數資料

| 型號: | AD7679ACP |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 18-Bit, 2.5 LSB INL, 570 kSPS SAR ADC |

| 中文描述: | 1-CH 18-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, QCC48 |

| 封裝: | MO-220-VKKD-2, LFCSP-48 |

| 文件頁數: | 5/28頁 |

| 文件大小: | 1186K |

| 代理商: | AD7679ACP |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

AD7679

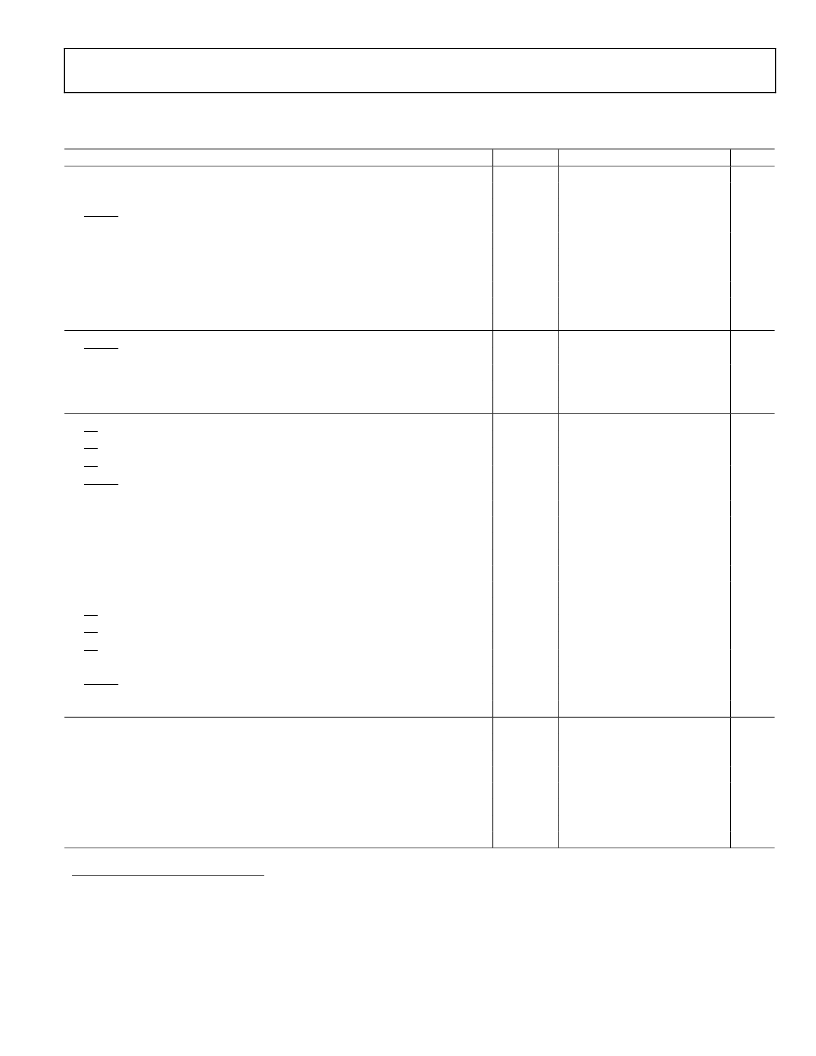

TIMING SPECIFICATIONS

Table 3. –40°C to +85°C, AVDD = DVDD = 5 V, OVDD = 2.7 V to 5.25 V, unless otherwise noted.

Parameter

Refer to Figure 32 and Figure 33

Convert Pulsewidth

Time between Conversions

CNVST LOW to BUSY HIGH Delay

BUSY HIGH All Modes Except Master Serial Read after Convert

Aperture Delay

End of Conversion to BUSY LOW Delay

Conversion Time

Acquisition Time

RESET Pulsewidth

Refer to Figure 34, Figure 35, and Figure 36 (Parallel Interface Modes)

CNVST LOW to Data Valid Delay

Data Valid to BUSY LOW Delay

Bus Access Request to Data Valid

Bus Relinquish Time

Refer to Figure 38 and Figure 39 (Master Serial Interface Modes)

1

CS LOW to SYNC Valid Delay

CS LOW to Internal SCLK Valid Delay

CS LOW to SDOUT Delay

CNVST LOW to SYNC Delay

SYNC Asserted to SCLK First Edge Delay

2

Internal SCLK Period

2

Internal SCLK HIGH

2

Internal SCLK LOW

2

SDOUT Valid Setup Time

2

SDOUT Valid Hold Time

2

SCLK Last Edge to SYNC Delay

2

CS HIGH to SYNC HI-Z

CS HIGH to Internal SCLK HI-Z

CS HIGH to SDOUT HI-Z

BUSY HIGH in Master Serial Read after Convert

2

CNVST LOW to SYNC Asserted Delay

SYNC Deasserted to BUSY LOW Delay

Refer to Figure 40 and Figure 41 (Slave Serial Interface Modes)

External SCLK Setup Time

External SCLK Active Edge to SDOUT Delay

SDIN Setup Time

SDIN Hold Time

External SCLK Period

External SCLK HIGH

External SCLK LOW

1

In serial interface modes, the SYNC, SCLK, and SDOUT timings are defined with a maximum load C

L

of 10 pF; otherwise, the load is 60 pF maximum.

2

In Serial Master Read during Convert mode. See

for Serial Master Read after Convert mode.

Table 4

Symbol

t

1

t

2

t

3

t

4

t

5

t

6

t

7

t

8

t

9

t

10

t

11

t

12

t

13

t

14

t

15

t

16

t

17

t

18

t

19

t

20

t

21

t

22

t

23

t

24

t

25

t

26

t

27

t

28

t

29

t

30

t

31

t

32

t

33

t

34

t

35

t

36

t

37

Min

10

1.75

10

250

10

20

5

3

25

12

7

4

2

3

5

3

5

5

25

10

10

Typ

2

525

See Table 4

1.5

25

Max

35

1.5

1.5

1.5

45

15

10

10

10

40

10

10

10

18

Unit

ns

μs

ns

μs

ns

ns

μs

ns

ns

μs

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

μs

ns

ns

ns

ns

ns

ns

ns

ns

Rev. 0 | Page 5 of 28

相關PDF資料 |

PDF描述 |

|---|---|

| AD7679ACPRL | 18-Bit, 2.5 LSB INL, 570 kSPS SAR ADC |

| AD7679AST | 18-Bit, 2.5 LSB INL, 570 kSPS SAR ADC |

| AD7679ASTRL | 18-Bit, 2.5 LSB INL, 570 kSPS SAR ADC |

| AD7675 | 16-Bit, 100 kSPS, Differential ADC |

| AD7675AST | 16-Bit, 100 kSPS, Differential ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7679ACPRL | 制造商:Analog Devices 功能描述:ADC Single SAR 570ksps 18-bit Parallel/Serial 48-Pin LFCSP EP T/R 制造商:Analog Devices 功能描述:ADC SGL SAR 570KSPS 18BIT PARALLEL/SERL 48LFCSP EP - Tape and Reel 制造商:Rochester Electronics LLC 功能描述:18-BIT,100KSPSSARADC - Tape and Reel |

| AD7679ACPZ | 功能描述:IC ADC 18BIT SAR W/BUFF 48LFCSP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:PulSAR® 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7679ACPZRL | 功能描述:IC ADC 18BIT SAR W/BUFF 48LFCSP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:PulSAR® 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7679AST | 制造商:Analog Devices 功能描述:ADC Single SAR 570ksps 18-bit Parallel/Serial 48-Pin LQFP 制造商:Analog Devices 功能描述:18BIT SAR ADC SMD 7679 LQFP48 |

| AD7679ASTRL | 制造商:Analog Devices 功能描述:ADC Single SAR 570ksps 18-bit Parallel/Serial 48-Pin LQFP T/R 制造商:Analog Devices 功能描述:ADC SGL SAR 570KSPS 18BIT PARALLEL/SERL 48LQFP - Tape and Reel |

發布緊急采購,3分鐘左右您將得到回復。