- 您現在的位置:買賣IC網 > PDF目錄2076 > IDT72T18125L4-4BB (IDT, Integrated Device Technology Inc)IC FIFO 524X18 2.5V 4NS 240BGA PDF資料下載

參數資料

| 型號: | IDT72T18125L4-4BB |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數: | 1/55頁 |

| 文件大小: | 0K |

| 描述: | IC FIFO 524X18 2.5V 4NS 240BGA |

| 標準包裝: | 1 |

| 系列: | 72T |

| 功能: | 異步,同步 |

| 存儲容量: | 9M(512K x 18) |

| 數據速率: | 10MHz |

| 訪問時間: | 3.4ns |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 240-BGA |

| 供應商設備封裝: | 240-PBGA(19x19) |

| 包裝: | 托盤 |

| 其它名稱: | 72T18125L4-4BB |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

1

FEBRUARY 2009

DSC-5909/19

2009 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice.

2.5 VOLT HIGH-SPEED TeraSync FIFO

18-BIT/9-BIT CONFIGURATIONS

2,048 x 18/4,096 x 9, 4,096 x 18/8,192 x 9, 8,192 x 18/16,384 x 9,

16,384 x 18/32,768 x 9, 32,768 x 18/65,536 x 9, 65,536 x 18/131,072 x 9,

131,072 x 18/262,144 x 9, 262,144 x 18/524,288 x 9, 524,288 x 18/1,048,576 x 9

IDT72T1845, IDT72T1855

IDT72T1865, IDT72T1875

IDT72T1885, IDT72T1895

IDT72T18105, IDT72T18115

IDT72T18125

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc. TeraSync FIFO is a trademark of Integrated Device Technology, Inc.

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

FEATURES:

Choose among the following memory organizations:

IDT72T1845

2,048 x 18/4,096 x 9

IDT72T1855

4,096 x 18/8,192 x 9

IDT72T1865

8,192 x 18/16,384 x 9

IDT72T1875

16,384 x 18/32,768 x 9

IDT72T1885

32,768 x 18/65,536 x 9

IDT72T1895

65,536 x 18/131,072 x 9

IDT72T18105

131,072 x 18/262,144 x 9

IDT72T18115

262,144 x 18/524,288 x 9

IDT72T18125

524,288 x 18/1,048,576 x 9

Up to 225 MHz Operation of Clocks

User selectable HSTL/LVTTL Input and/or Output

Read Enable & Read Clock Echo outputs aid high speed operation

User selectable Asynchronous read and/or write port timing

2.5V LVTTL or 1.8V, 1.5V HSTL Port Selectable Input/Ouput voltage

3.3V Input tolerant

Mark & Retransmit, resets read pointer to user marked position

Write Chip Select (WCS) input enables/disables Write operations

Read Chip Select (RCS) synchronous to RCLK

Programmable Almost-Empty and Almost-Full flags, each flag can

default to one of eight preselected offsets

Program programmable flags by either serial or parallel means

Selectable synchronous/asynchronous timing modes for Almost-

Empty and Almost-Full flags

Separate SCLK input for Serial programming of flag offsets

User selectable input and output port bus-sizing

- x9 in to x9 out

- x9 in to x18 out

- x18 in to x9 out

- x18 in to x18 out

Big-Endian/Little-Endian user selectable byte representation

Auto power down minimizes standby power consumption

Master Reset clears entire FIFO

Partial Reset clears data, but retains programmable settings

Empty, Full and Half-Full flags signal FIFO status

Select IDT Standard timing (using EF and FF flags) or First Word

Fall Through timing (using

OR and IR flags)

Output enable puts data outputs into high impedance state

JTAG port, provided for Boundary Scan function

Available in 144-pin (13mm x 13mm) or 240-pin (19mm x 19mm)

PlasticBall Grid Array (PBGA)

Easily expandable in depth and width

Independent Read and Write Clocks (permit reading and writing

simultaneously)

High-performance submicron CMOS technology

Industrial temperature range (–40

°°°°°C to +85°°°°°C) is available

Green parts are available, see ordering information

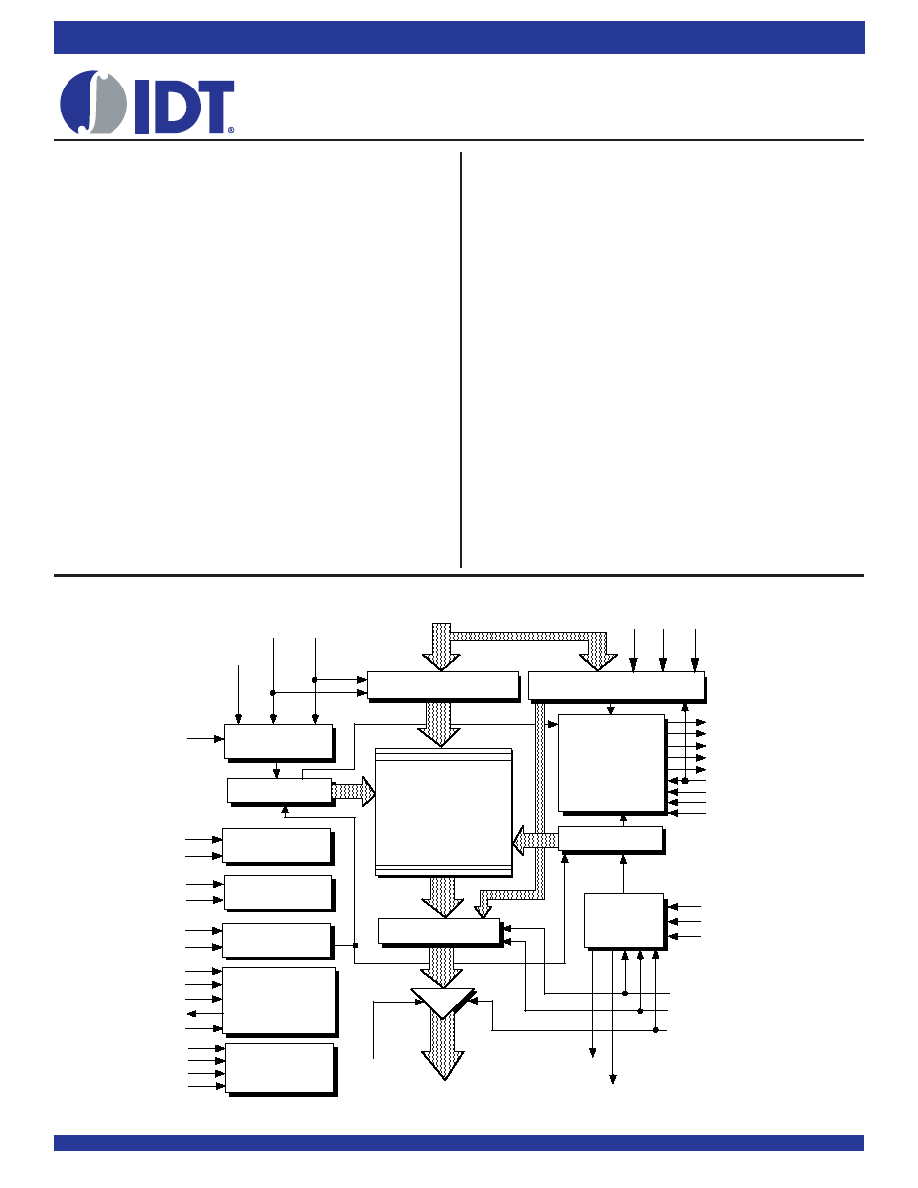

INPUT REGISTER

OUTPUT REGISTER

RAM ARRAY

2,048 x 18 or 4,096 x 9

4,096 x 18 or 8,192 x 9

8,192 x 18 or 16,384 x 9

16,384 x 18 or 32,768 x 9

32,768 x 18 or 65,536 x 9

65,536 x 18 or 131,072 x 9

131,072 x 18 or 262,144 x 9

262,144 x 18 or 524,288 x 9

524,288 x 18 or 1,048,576 x 9

FLAG

LOGIC

FF/IR

PAF

EF/OR

PAE

HF

READ POINTER

READ

CONTROL

LOGIC

WRITE CONTROL

LOGIC

WRITE POINTER

RESET

LOGIC

WEN WCLK/WR

D0 -Dn (x18 or x9)

LD

MRS

REN

RCLK/RD

OE

Q0 -Qn (x18 or x9)

OFFSET REGISTER

PRS

FWFT/SI

SEN

RT

5909 drw01

BUS

CONFIGURATION

CONTROL

LOGIC

BE

OW

IP

PFM

FSEL0

FSEL1

IW

MARK

SCLK

RCS

JTAG CONTROL

(BOUNDARY SCAN)

TCK

TMS

TDO

TDI

TRST

ASYR

WCS

ERCLK

EREN

HSTL I/0

CONTROL

Vref

WHSTL

RHSTL

ASYW

SHSTL

FUNCTIONAL BLOCK DIAGRAM

相關PDF資料 |

PDF描述 |

|---|---|

| IDT72T36125L5BBI | IC FIFO 524X18 5NS 240BGA |

| IDT72T36135ML5BBG | IC FIFO 1MX18 5NS 240BGA |

| IDT72T72115L5BBI | IC FIFO 131072X72 5NS 324-BGA |

| IDT72V06L15J | IC ASYNCH 8192X18 15NS 32PLCC |

| IDT72V2105L15PFI | IC FIFO SUPERSYNCII 15NS 64-TQFP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| IDT72T18125L4-4BBG | 功能描述:IC FIFO 524X18 2.5V 4NS 240BGA RoHS:是 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72T 標準包裝:90 系列:74ABT 功能:同步,雙端口 存儲容量:4.6K(64 x 36 x2) 數據速率:67MHz 訪問時間:- 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:120-LQFP 裸露焊盤 供應商設備封裝:120-HLQFP(14x14) 包裝:托盤 產品目錄頁面:1005 (CN2011-ZH PDF) 其它名稱:296-3984 |

| IDT72T18125L5BB | 功能描述:IC FIFO 524X18 2.5V 5NS 240BGA RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72T 標準包裝:15 系列:74F 功能:異步 存儲容量:256(64 x 4) 數據速率:- 訪問時間:- 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:24-DIP(0.300",7.62mm) 供應商設備封裝:24-PDIP 包裝:管件 其它名稱:74F433 |

| IDT72T18125L5BBGI | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO 524X18 2.5V 5NS 240BGA |

| IDT72T18125L5BBI | 功能描述:IC FIFO 524X18 2.5V 5NS 240BGA RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72T 標準包裝:90 系列:74ABT 功能:同步,雙端口 存儲容量:4.6K(64 x 36 x2) 數據速率:67MHz 訪問時間:- 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:120-LQFP 裸露焊盤 供應商設備封裝:120-HLQFP(14x14) 包裝:托盤 產品目錄頁面:1005 (CN2011-ZH PDF) 其它名稱:296-3984 |

| IDT72T18125L6-7BB | 功能描述:IC FIFO 524X18 2.5V 6-7NS 240BGA RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72T 標準包裝:15 系列:74F 功能:異步 存儲容量:256(64 x 4) 數據速率:- 訪問時間:- 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:24-DIP(0.300",7.62mm) 供應商設備封裝:24-PDIP 包裝:管件 其它名稱:74F433 |

發布緊急采購,3分鐘左右您將得到回復。