- 您現在的位置:買賣IC網 > Datasheet目錄40 > ISL25700FRUZ-TK (Intersil)IC TEMP SWITCH MFET DRVR 10TQFN Datasheet資料下載

參數資料

| 型號: | ISL25700FRUZ-TK |

| 廠商: | Intersil |

| 文件頁數: | 7/18頁 |

| 文件大小: | 441K |

| 描述: | IC TEMP SWITCH MFET DRVR 10TQFN |

| 標準包裝: | 1,000 |

| 功能: | 溫度監控系統(傳感器),溫度開關 |

| 傳感器類型: | 外部 |

| 感應溫度: | 40°C ~ 110°C 跳變點 |

| 精確度: | ±3°C |

| 拓撲: | 比較器,電壓基準 |

| 輸出類型: | 電壓 |

| 輸出警報: | 無 |

| 輸出風扇: | 無 |

| 電源電壓: | 3 V ~ 15 V |

| 工作溫度: | -40°C ~ 125°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 10-UFQFN |

| 供應商設備封裝: | 10-UTQFN(2.1x1.6) |

| 包裝: | 帶卷 (TR) |

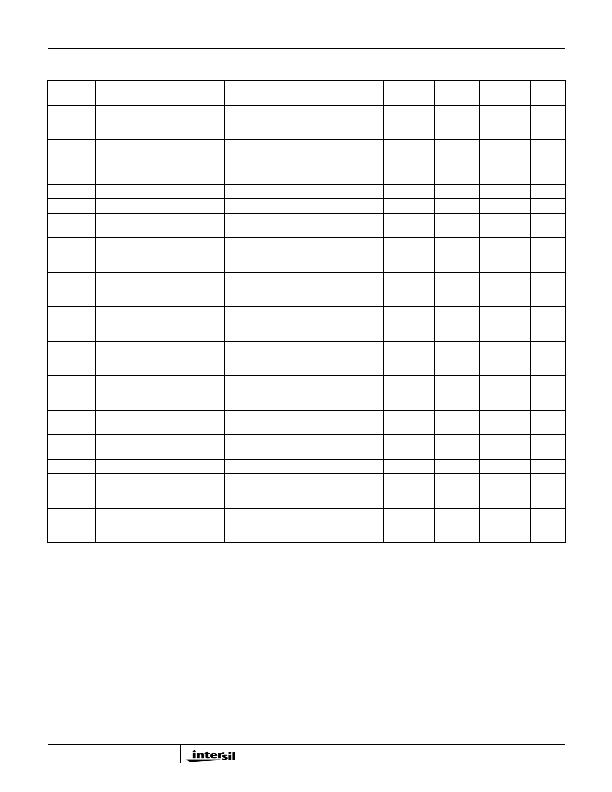

ISL25700

7

FN6885.0

September 3, 2010

t

AA

(Note 11)

SCL Falling Edge to SDA

Output Data Valid

SCL falling edge crossing 30% of V

I2C

,

until SDA exits the 30% to 70% of

V

I2C

window

900

ns

t

BUF

(Note 11)

Time the Bus Must be Free

Before the Start of a New

Transmission

SDA crossing 70% of V

I2C

during a

STOP condition, to SDA crossing 70%

of V

I2C

during the following START

condition

1300

ns

t

LOW

Clock LOW Time

Measured at the 30% of V

I2C

crossing

1300

ns

t

HIGH

Clock HIGH Time

Measured at the 70% of V

I2C

crossing

600

ns

t

SU:STA

START Condition Setup Time SCL rising edge to SDA falling edge.

Both crossing 70% of V

I2C

.

600

ns

t

HD:STA

START Condition Hold Time

From SDA falling edge crossing 30%

of V

I2C

to SCL falling edge crossing

70% of V

I2C

600

ns

t

SU:DAT

Input Data Setup Time

From SDA exiting the 30% to 70% of

V

I2C

window, to SCL rising edge

crossing 30% of V

I2C

100

ns

t

HD:DAT

Input Data Hold Time

From SCL falling edge crossing 70% of

V

I2C

to SDA entering the 30% to 70%

of V

I2C

window

0

ns

t

SU:STO

STOP Condition Setup Time

From SCL rising edge crossing 70% of

V

I2C

, to SDA rising edge crossing 30%

of V

I2C

600

ns

t

DH

Output Data Hold Time

From SCL falling edge crossing 30% of

V

I2C

, until SDA enters the 30% to

70% of V

I2C

window

0

ns

t

R

SDA and SCL Rise Time

From 30% to 70% of V

I2C

20 +

0.1 * Cb

250

ns

t

F

SDA and SCL Fall Time

From 70% to 30% of V

I2C

20 +

0.1 * Cb

250

ns

Cb

Capacitive Loading of SDA or SCL Total on-chip and off-chip

10

400

pF

Rpu

(Note 11)

SDA and SCL Bus Pull-Up

Resistor Off-Chip

Maximum is determined by t

R

and t

F

.

For Cb = 400pF, max is about 2~2.5k?

For Cb = 40pF, max is about 15~20k?/DIV>

1

k?/DIV>

t

WC

(Notes

11, 12)

Non-Volatile Write Cycle Time

15

20

ms

NOTES:

6. Typical values are for T

A

= +25癈 and 12V supply voltage.

7. LSB: [VDAC

255

VDAC

0

]/255. VDAC

255

and VDAC

0

are the DAC output voltage when DAC register set to FF hex and 00 hex

respectively.

8. DNL = [VDAC

i

VDAC

i-1

]/LSB-1, for i = 1 to 255. i is the DAC register setting.

9. INL = [VDAC

i

(i " LSB + VDAC

0

)]/LSB for i = 1 to 255.

10.

for i = 1 to 255 decimal, T = -40癈 to +125癈, referenced to 40癈.

11. Limits established by characterization and are not production tested.

12. t

WC

is the time from a valid STOP condition at the end of a Write sequence of a I

2

C serial interface Write operation, to the

end of the self-timed internal non-volatile write cycle. The Busy Polling method can be used to determine the end of the

non-volatile write cycle.

13. Parameters with MIN and/or MAX limits are 100% tested at +25癈, unless otherwise specified. Temperature limits established

by characterization and are not production tested.

14. B

25/85

is a thermistor material specific constant; represents the slope of the Resistance vs. Temperature curve.

Operating Specifications Over the recommended operating conditions unless otherwise specified. Boldface limits

apply over the operating temperature range, -40癈 to +125癈. (Continued)

SYMBOL

PARAMETER

TEST CONDITIONS

MIN

(Note 13)

TYP

(Note 6)

MAX

(Note 13) UNITS

TC

V

VDAC

i

T

( ) VDAC

i

40癈

(

)

VDAC

i

40癈

(

)

------------------------------------------------------------------------ -

10

6

T 40

(

)癈

--------------------------- -

?/DIV>

=

相關PDF資料 |

PDF描述 |

|---|---|

| ISL6150IB | IC CTRLR HOT PLUG NEG VOLT 8SOIC |

| ISL6151IB-T | IC CTRLR HOT PLUG NEG VOLT 8SOIC |

| ISL6160CB-T | IC CTRLR BULK/AUXILIARY 14-SOIC |

| ISL6161CB-T | IC CTRLR PWR DISTRIB DUAL 14SOIC |

| ISL6173DRZA-T | IC CTRLR HOT SWAP DUAL LV 28-QFN |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ISL26102 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Low-Noise 24-bit Delta Sigma ADC |

| ISL26102AVZ | 制造商:Intersil Corporation 功能描述:LOW-NOISE 24-BIT DELTA SIGMA ADC, OPERATION TO 4KSPS, 24L TS - Bulk 制造商:Intersil Corporation 功能描述:IC ADC 24BIT SRL 2CH 24-TSSOP 制造商:Intersil 功能描述:LOW-NOISE 24Bit ADC- 4KSPS IC------------ 制造商:INTERSIL 功能描述:ISL26102 Series Dual Ch 24-bit Delta Sigma Analog to Digital Converter TSSOP-24 |

| ISL26102AVZ-T | 制造商:Intersil Corporation 功能描述:LOW-NOISE 24-BIT DELTA SIGMA ADC, OPERATION TO 4KSPS, 24L TS - Tape and Reel 制造商:Intersil Corporation 功能描述:IC ADC 24BIT SRL 2CH 24-TSSOP 制造商:Intersil 功能描述:LOW-NOISE 24Bit ADC- 4KSPS IC------------ |

| ISL26102AVZ-T7A | 功能描述:模數轉換器 - ADC LOW-NOISE 24Bit ADC 4KSPS IC RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| ISL26104 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Low-Noise 24-bit Delta Sigma ADC |

發布緊急采購,3分鐘左右您將得到回復。