- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄192295 > S29CD032J1MQFN133 (SPANSION LLC) 1M X 32 FLASH 2.7V PROM, 54 ns, PQFP80 PDF資料下載

參數(shù)資料

| 型號(hào): | S29CD032J1MQFN133 |

| 廠商: | SPANSION LLC |

| 元件分類: | PROM |

| 英文描述: | 1M X 32 FLASH 2.7V PROM, 54 ns, PQFP80 |

| 封裝: | LEAD FREE, PLASTIC, MO-108CB-1, QFP-80 |

| 文件頁數(shù): | 19/78頁 |

| 文件大小: | 1825K |

| 代理商: | S29CD032J1MQFN133 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁

24

S29CD-J & S29CL-J Flash Family

S29CD-J_CL-J_00_B1 September27,2006

Prel imi n ary

8.4.1

2-, 4-, 8- Double Word Linear Burst Operation

In a linear burst read operation, a fixed number of words (2, 4, or 8 double words) are read from

consecutive addresses that are determined by the group within which the starting address falls.

Note that 1 double word = 32 bits. See Table 8.2 for all valid burst output sequences.

The IND/WAIT# signal, or End of Burst Indicator signal, transitions active (VIL) during the last

transfer of data in a linear burst read before a wrap around. This transition indicates that the

system should initiate another ADV# to start the next burst access. If the system continues to

clock the device, the next access wraps around to the starting address of the previous burst ac-

cess. The IND/WAIT# signal is floating when not active.

The IND/WAIT# signal is controlled by the OE# signal. If OE# is at VIH, the IND/WAIT# signal

floats and is not driven. If OE# is at VIL, the IND/ WAIT# signal is driven at VIH until it transitions

to VIL, indicating the end of the burst sequence. Table 8.3 lists the valid combinations of the Con-

figuration Register bits that impact the IND/WAIT# timing. See Figure 8.3 for the IND/WAIT#

timing diagram.

Notes:

1. The default configuration in the Control Register for Bit 6 is "1," indicating that the device delivers data on the rising edge

of the CLK signal.

2. The device is capable of holding data for one CLK cycle.

3. If RESET# is asserted low during a burst access, the burst access is immediately terminated and the device defaults

back to asynchronous read mode. When this happens, the DQ data bus signal floats and the Configuration Register

contents are reset to their default conditions.

4. CE# must meet the required burst read setup times for burst cycle initiation. If CE# is taken to VIH at any time during

the burst linear or burst cycle, the device immediately exits the burst sequence and floats the DQ bus signal.

5. Restarting a burst cycle is accomplished by taking CE# and ADV# to VIL.

6. A burst access is initiated and the address is latched on the first rising CLK edge when ADV# is active or upon a rising

ADV# edge, whichever occurs first. If the ADV# signal is taken to VIL prior to the end of a linear burst sequence, the

previous address is discarded and subsequent burst transfers are invalid. A new burst is initiated when ADV# transitions

back to VIH before a clock edge.

7. The OE# (Output Enable) pin is used to enable the linear burst data on the DQ data bus pin. De-asserting the OE# pin

to VIH during a burst operation floats the data bus, but the device continues to operate internally as if the burst sequence

continues until the linear burst is complete. The OE# pin does not halt the burst sequence, The DQ bus remains in the

float state until OE# is taken to VIL.

8. Halting the burst sequence is accomplished by either taking CE# to VIH or re-issuing a new ADV# pulse.

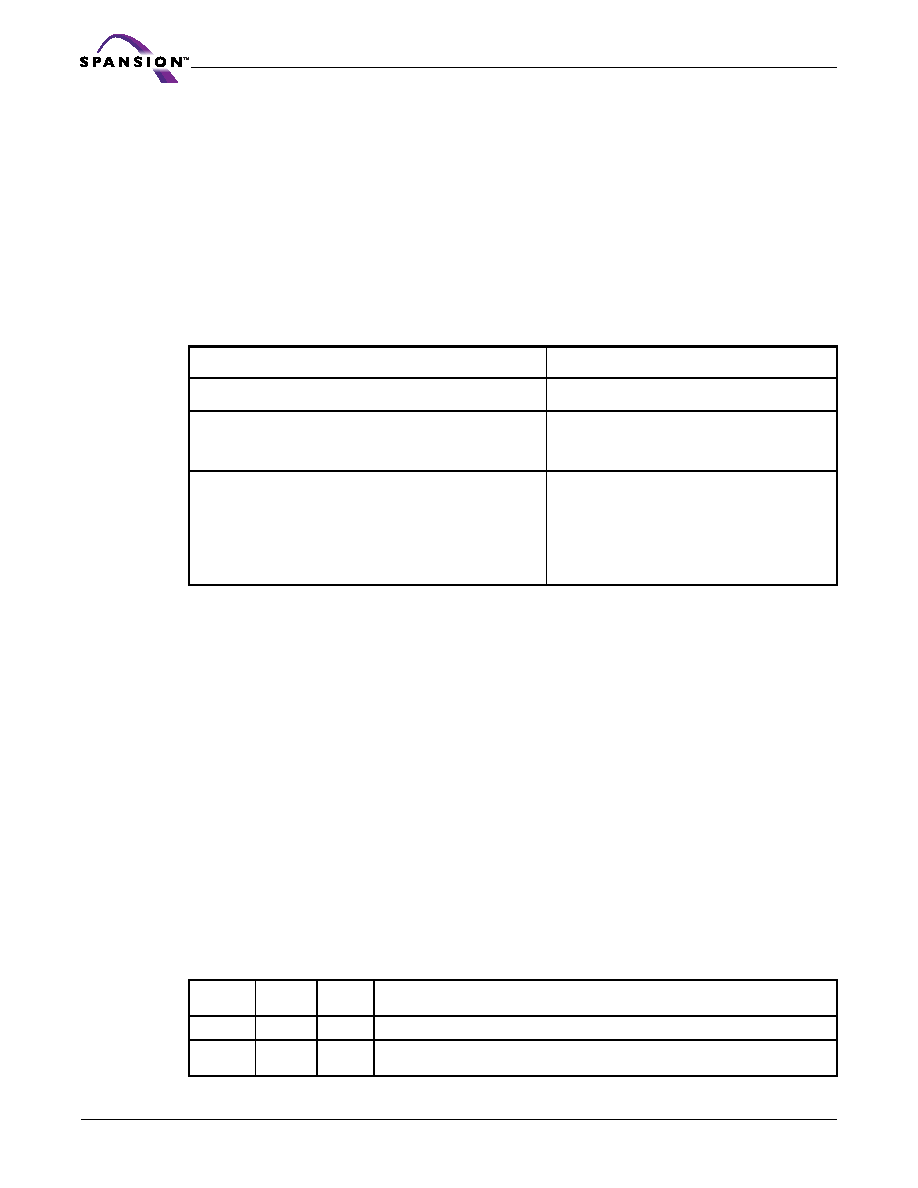

Table 8.2 32- Bit Linear and Burst Data Order

Data Transfer Sequence (Independent of the WORD# pin)

Output Data Sequence (Initial Access Address)

(x16)

Two Linear Data Transfers

0-1 (A0 = 0)

1-0 (A0 = 1)

Four Linear Data Transfers

0-1-2-3 (A0:A-1/A1-A0 = 00)

1-2-3-0 (A0:A-1/A1-A0 = 01)

2-3-0-1 (A:A-1/A1-A0 = 10)

3-0-1-2 (A0:A-1/A1-A0 = 11)

Eight Linear Data Transfers

0-1-2-3-4-5-6-7 (A1:A-1A2-A0 = 000)

1-2-3-4-5-6-7-0 (A1:A-1/A2-A0 = 001)

2-3-4-5-6-7-0-1 (A1:A-1/A2-A0 = 010)

3-4-5-6-7-0-1-2 (A1:A-1/A2-A0 = 011)

4-5-6-7-0-1-2-3 (A1:A-1/A2-A0 = 100)

5-6-7-0-1-2-3-4 (A1:A-1/A2-A0 = 101)

6-7-0-1-2-3-4-5 (A1:A-1/A2-A0 = 110)

7-0-1-2-3-4-5-6 (A1:A-1/A2-A0 = 111)

Table 8.3 Valid Configuration Register Bit Definition for IND/WAIT#

CR9

(DOC)

CR8

(WC)

CR6

(CC)

Definition

00

1

IND/WAIT# = VIL for 1-CLK cycle, Active on last transfer, Driven on rising CLK edge

01

1

IND/WAIT# = VIL for 1-CLK cycle, Active on second to last transfer, Driven on rising

CLK edge

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S29CL016J0JQFI100 | 512K X 32 FLASH 3.3V PROM, 54 ns, PQFP80 |

| S29CL016J0MFAI113 | 512K X 32 FLASH 3.3V PROM, 54 ns, PBGA80 |

| S29CL016J0PQFI102 | 512K X 32 FLASH 3.3V PROM, 54 ns, PQFP80 |

| S29CL016J0MFAM100 | 512K X 32 FLASH 3.3V PROM, 54 ns, PBGA80 |

| S29CL016J0PFFM102 | 512K X 32 FLASH 3.3V PROM, 54 ns, PBGA80 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S29CL016J0JQFM030 | 制造商:Spansion 功能描述:FLASH PARALLEL 3.3V 16MBIT 512KX32 54NS 80PQFP - Trays |

| S29CL016J0JQFM030P | 制造商:Spansion 功能描述:AUTO 3.3V 512KX32 FLASH - Trays |

| S29CL016J0JQFM030U | 制造商:Spansion 功能描述:32M (4MX8/2MX16) 3V REG, MIRRORBIT, TOP, FBGA48, IND - Trays |

| S29CL016J0JQFM03U | 制造商:Spansion 功能描述:32M (4MX8/2MX16) 3V REG, MIRRORBIT, TOP, FBGA48, IND - Trays |

| S29CL016J0MQFM030 | 制造商:Spansion 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。