- 您現在的位置:買賣IC網 > PDF目錄382648 > TMX320F2810PBKA (Texas Instruments, Inc.) DIGITAL SIGNAL PROCESSORS PDF資料下載

參數資料

| 型號: | TMX320F2810PBKA |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數字信號處理 |

| 英文描述: | DIGITAL SIGNAL PROCESSORS |

| 中文描述: | 數字信號處理器 |

| 文件頁數: | 51/103頁 |

| 文件大小: | 1341K |

| 代理商: | TMX320F2810PBKA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁當前第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁

TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B

–

APRIL 2001

–

REVISED SEPTEMBER 2001

51

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251

–

1443

watchdog block

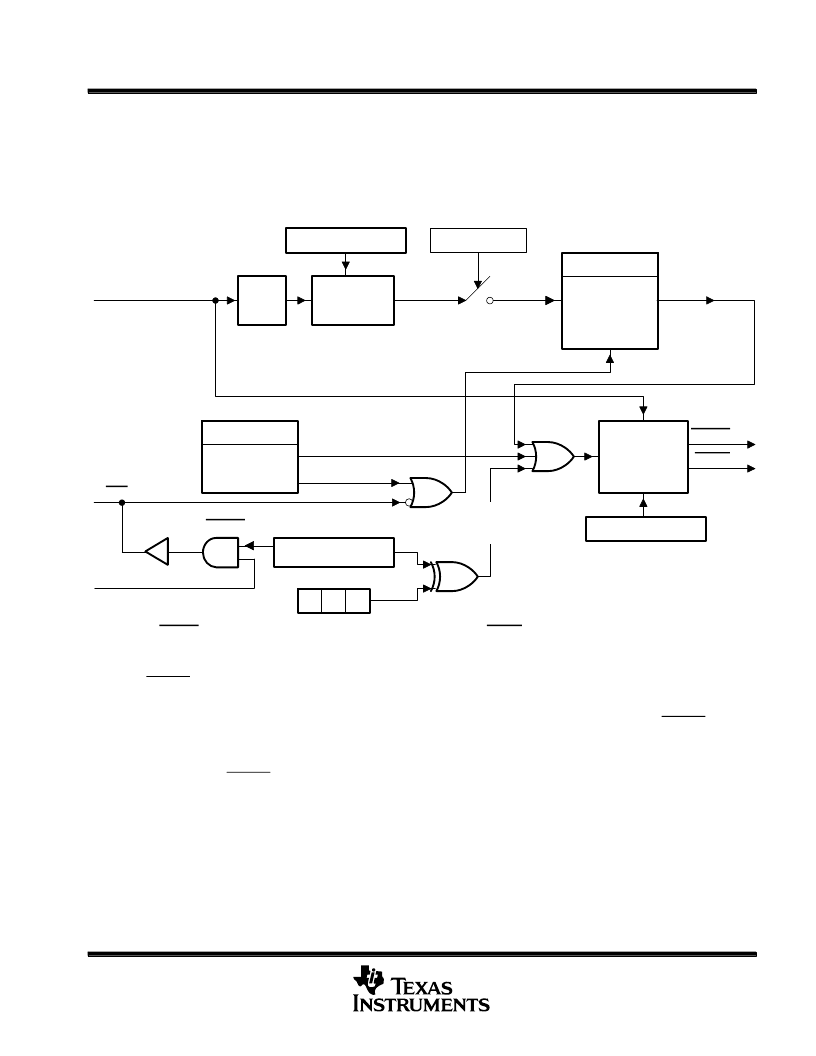

The watchdog block on the F2810 and F2812 is identical to the one used on the 240x devices. The watchdog

module generates an output pulse, 512 oscillator clocks wide (OSCCLK), whenever the 8-bit watchdog up

counter has reached its maximum value. To prevent this, the user disables the counter or the software must

periodically write a 0x55 + 0xAA sequence into the watchdog key register which will reset the watchdog counter.

Figure 11 shows the various functional blocks within the watchdog module.

/512

OSCCLK

WDCR (WDPS(2:0))

WDCLK

WDCNTR(7:0)

WDKEY(7:0)

Bad Key

Good Key

1

0

1

WDCR (WDCHK(2:0))

Bad

WDCHK

Key

WDCR (WDDIS)

Clear Counter

SCSR (WDENINT)

Watchdog

Prescaler

Generate

Output Pulse

(512 OSCCLKs)

8-Bit

Watchdog

Counter

CLR

WDRST

WDINT

Watchdog

55 + AA

Key Detector

XRS

XPPLDIS

WDRST

O.C.

NOTE A: The WDRST signal is driven low for 512 OSCCLK cycles (similarly for the WDINT signal if enabled).

Figure 11. Watchdog Module

The WDINT signal enables the watchdog to be used as a wakeup from IDLE/STANDBY mode timer.

In STANDBY mode, all peripherals are turned off on the device. The only peripheral that remains functional is

the watchdog. The WATCHDOG module will run off the PLL clock or the oscillator clock. The WDINT signal is

fed to the LPM block so that it can wake the device from STANDBY (if enabled). Refer to

”

Low-Power Modes

Block

”

section of this data sheet for more details.

In IDLE mode, the WDINT signal can generate an interrupt to the CPU, via the PIE, to take the CPU out of IDLE

mode.

In HALT mode, this feature cannot be used because the oscillator (and PLL) are turned off and hence so is the

WATCHDOG.

P

相關PDF資料 |

PDF描述 |

|---|---|

| TMP320F2810PBKA | DIGITAL SIGNAL PROCESSORS |

| TMX320F2810PBKAEP | Digital Signal Processors |

| TMP320F2810PBKAEP | Digital Signal Processors |

| TMX320F2810PBKS | DIGITAL SIGNAL PROCESSORS |

| TMP320F2810PBKS | DIGITAL SIGNAL PROCESSORS |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TMX320F2810PBKAEP | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Digital Signal Processors |

| TMX320F2810PBKS | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSORS |

| TMX320F2810PGFA | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSORS |

| TMX320F2810PGFAEP | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Digital Signal Processors |

| TMX320F2810PGFS | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSORS |

發布緊急采購,3分鐘左右您將得到回復。