- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298319 > 3D7323Z-10 (DATA DELAY DEVICES INC) MONOLITHIC TRIPLE FIXED DELAY LINE PDF資料下載

參數(shù)資料

| 型號(hào): | 3D7323Z-10 |

| 廠商: | DATA DELAY DEVICES INC |

| 元件分類: | 延遲線 |

| 英文描述: | MONOLITHIC TRIPLE FIXED DELAY LINE |

| 中文描述: | ACTIVE DELAY LINE, TRUE OUTPUT, PDSO8 |

| 封裝: | 0.150 INCH, ROHS COMPLIANT, SOIC-8 |

| 文件頁(yè)數(shù): | 1/4頁(yè) |

| 文件大小: | 252K |

| 代理商: | 3D7323Z-10 |

3D7323

MONOLITHIC TRIPLE

FIXED DELAY LINE

(SERIES 3D7323)

FEATURES

All-silicon, low-power CMOS technology

TTL/CMOS compatible inputs and outputs

Vapor phase, IR and wave solderable

Low ground bounce noise

Leading- and trailing-edge accuracy

Delay range: 6 through 6000ns

Delay tolerance: 2% or 1.0ns

Temperature stability:

±3% typ (-40C to 85C)

Vdd stability:

±1% typical (4.75V to 5.25V)

Minimum input pulse width: 20% of total delay

FUNCTIONAL DESCRIPTION

The 3D7323 Triple Delay Line product family consists of fixed-delay

CMOS integrated circuits. Each package contains three matched,

independent delay lines. Delay values can range from 6ns through

6000ns. The input is reproduced at the output without inversion,

shifted in time as per the user-specified dash number. The 3D7323

is TTL- and CMOS-compatible, capable of driving ten 74LS-type

loads, and features both rising- and falling-edge accuracy.

The all-CMOS 3D7323 integrated circuit has been designed as a

reliable, economic alternative to hybrid TTL fixed delay lines. It is

offered in a space saving surface mount 8-pin SOIC.

PACKAGES

1

2

3

4

8

7

6

5

I1

I2

I3

GND

VDD

O1

O2

O3

3D7323Z SOIC

(150 Mil)

PIN DESCRIPTIONS

I1

Delay Line 1 Input

I2

Delay Line 2 Input

I3

Delay Line 3 Input

O1

Delay Line 1 Output

O2

Delay Line 2 Output

O3

Delay Line 3 Output

VDD

+5 Volts

GND

Ground

N/C

No Connection

For mechanical dimensions, click

For package marking details, click

here.

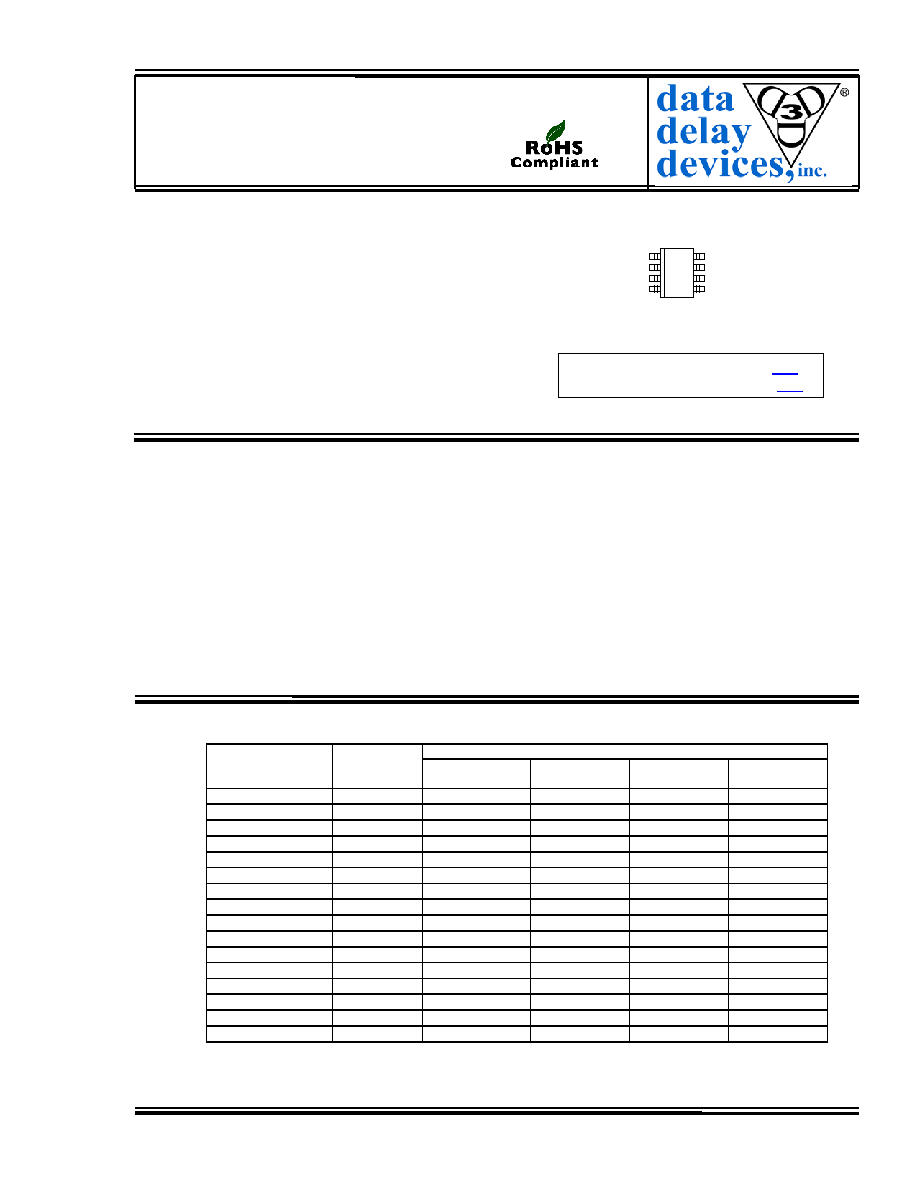

TABLE 1: PART NUMBER SPECIFICATIONS

DELAY

INPUT RESTRICTIONS

PART NUMBER

PER LINE

(ns)

Max Operating

Frequency

Absolute Max

Oper. Freq.

Min Operating

Pulse Width

Absolute Min

Oper. P.W.

3D7323Z-6

6

± 1.0

55.5 MHz

125.0 MHz

9.0 ns

4.0 ns

3D7323Z-8

8

± 1.0

41.6 MHz

111.0 MHz

12.0 ns

4.5 ns

3D7323Z-10

10

± 1.0

33.3 MHz

100.0 MHz

15.0 ns

5.0 ns

3D7323Z-15

15

± 1.0

22.2 MHz

100.0 MHz

22.5 ns

5.0 ns

3D7323Z-20

20

± 1.0

16.7 MHz

100.0 MHz

30.0 ns

5.0 ns

3D7323Z-25

25

± 1.0

13.3 MHz

83.3 MHz

37.5 ns

6.0 ns

3D7323Z-30

30

± 1.0

11.1 MHz

71.4 MHz

45.0 ns

7.0 ns

3D7323Z-40

40

± 1.0

8.33 MHz

62.5 MHz

60.0 ns

8.0 ns

3D7323Z-50

50

± 1.0

6.67 MHz

50.0 MHz

75.0 ns

10.0 ns

3D7323Z-100

100

± 2.0

3.33 MHz

25.0 MHz

150.0 ns

20.0 ns

3D7323Z-200

200

± 4.0

1.67 MHz

12.5 MHz

300.0 ns

40.0 ns

3D7323Z-500

500

± 10.0

0.67 MHz

5.00 MHz

750.0 ns

100.0 ns

3D7323Z-1000

1000

± 20

0.33 MHz

2.50 MHz

1500.0 ns

200.0 ns

3D7323Z-2000

2000

± 40

0.17 MHz

1.25 MHz

3000.0 ns

400.0 ns

3D7323Z-5000

5000

± 100

0.07 MHz

0.50 MHz

7500.0 ns

1000.0 ns

3D7323Z-6000

6000

± 120

0.05 MHz

0.42 MHz

9000.0 ns

1200.0 ns

NOTE: Any delay between 10 and 6000 ns not shown is also available.

2007 Data Delay Devices

Doc #06015

DATA DELAY DEVICES, INC.

1

6/25/2007

3 Mt. Prospect Ave. Clifton, NJ 07013

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 3D7323Z-100 | MONOLITHIC TRIPLE FIXED DELAY LINE |

| 3D7323Z-1000 | MONOLITHIC TRIPLE FIXED DELAY LINE |

| 3D7323Z-15 | MONOLITHIC TRIPLE FIXED DELAY LINE |

| 3D7323Z-20 | MONOLITHIC TRIPLE FIXED DELAY LINE |

| 3D7323Z-200 | MONOLITHIC TRIPLE FIXED DELAY LINE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 3D7323Z-100 | 制造商:DATADELAY 制造商全稱:Data Delay Devices, Inc. 功能描述:MONOLITHIC TRIPLE FIXED DELAY LINE |

| 3D7323Z-1000 | 制造商:DATADELAY 制造商全稱:Data Delay Devices, Inc. 功能描述:MONOLITHIC TRIPLE FIXED DELAY LINE |

| 3D7323Z-15 | 制造商:DATADELAY 制造商全稱:Data Delay Devices, Inc. 功能描述:MONOLITHIC TRIPLE FIXED DELAY LINE |

| 3D7323Z-20 | 制造商:DATADELAY 制造商全稱:Data Delay Devices, Inc. 功能描述:MONOLITHIC TRIPLE FIXED DELAY LINE |

| 3D7323Z-200 | 制造商:DATADELAY 制造商全稱:Data Delay Devices, Inc. 功能描述:MONOLITHIC TRIPLE FIXED DELAY LINE |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。