- 您現在的位置:買賣IC網 > PDF目錄30744 > 54ACT715-RS (NATIONAL SEMICONDUCTOR CORP) SPECIALTY CONSUMER CIRCUIT, PDSO20 PDF資料下載

參數資料

| 型號: | 54ACT715-RS |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO20 |

| 封裝: | SOIC-20 |

| 文件頁數: | 1/16頁 |

| 文件大小: | 323K |

| 代理商: | 54ACT715-RS |

LM1882

54ACT715

LM1882-R

54ACT715-R Programmable Video Sync

Generator

General Description

The ’ACT715/LM1882 and ’ACT715-R/LM1882-R are 20-pin

TTL-input compatible devices capable of generating Hori-

zontal, Vertical and Composite Sync and Blank signals for

televisions and monitors. All pulse widths are completely de-

finable by the user. The devices are capable of generating

signals for both interlaced and noninterlaced modes of op-

eration. Equalization and serration pulses can be introduced

into the Composite Sync signal when needed.

Four additional signals can also be made available when

Composite Sync or Blank are used. These signals can be

used to generate horizontal or vertical gating pulses, cursor

position or vertical Interrupt signal.

These devices make no assumptions concerning the system

architecture. Line rate and field/frame rate are all a function

of the values programmed into the data registers, the status

register, and the input clock frequency.

The ’ACT715/LM1882 is mask programmed to default to a

Clock Disable state. Bit 10 of the Status Register, Register 0,

defaults to a logic “0”. This facilitates (re)programming be-

fore operation.

The ’ACT715-R/LM1882-R is the same as the ’ACT715/

LM1882 in all respects except that the ’ACT715-R/

LM1882-R is mask programmed to default to a Clock En-

abled state. Bit 10 of the Status Register defaults to a logic

“1”. Although completely (re)programmable, the ’ACT715-R/

LM1882-R version is better suited for applications using the

default 14.31818 MHz RS-170 register values. This feature

allows power-up directly into operation, following a single

CLEAR pulse.

Features

n Maximum Input Clock Frequency > 130 MHz

n Interlaced and non-interlaced formats available

n Separate or composite horizontal and vertical Sync and

Blank signals available

n Complete control of pulse width via register

programming

n All inputs are TTL compatible

n 8 mA drive on all outputs

n Default RS170/NTSC values mask programmed into

registers

n 4 KV minimum ESD immunity

n ’ACT715-R/LM1882-R is mask programmed to default to

a Clock Enable state for easier start-up into

14.31818 MHz RS170 timing

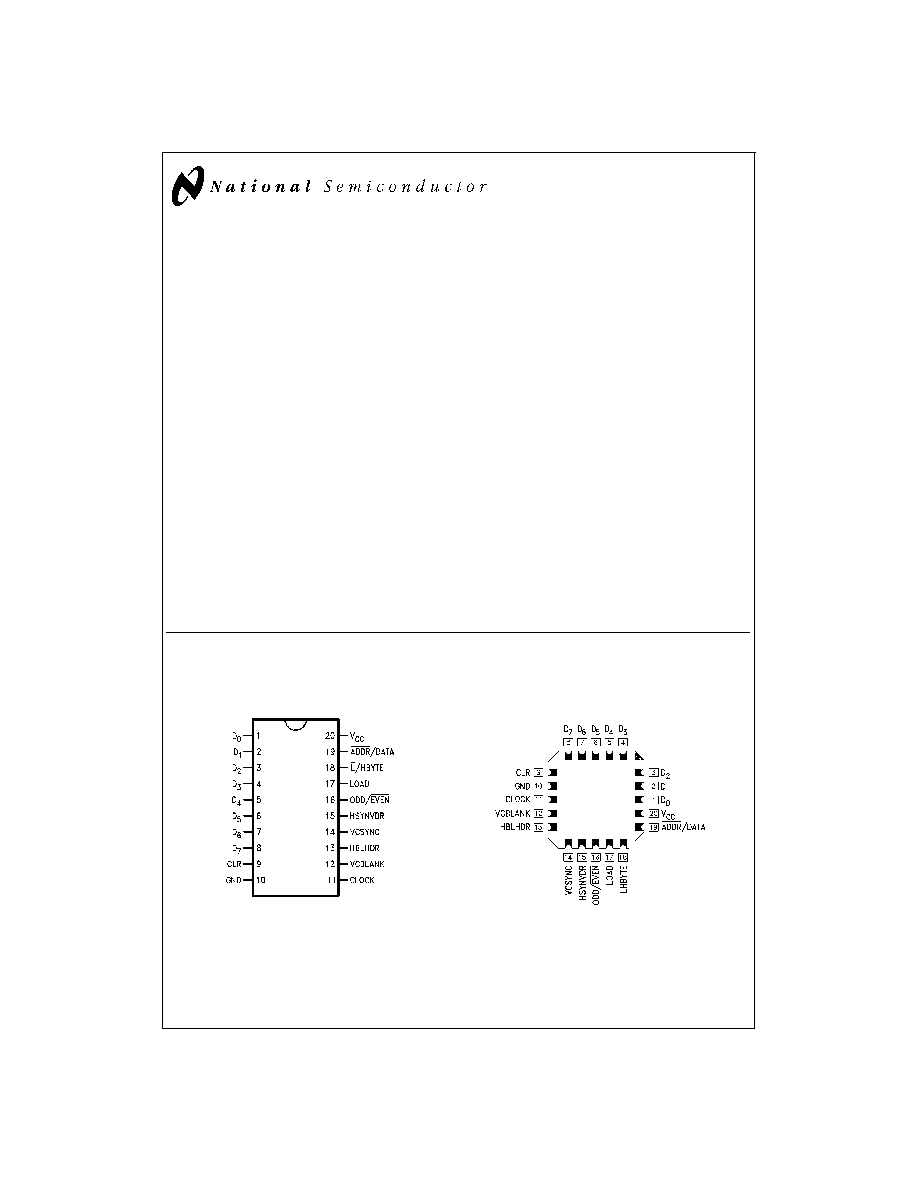

Connection Diagrams

TRI-STATE is a registered trademark of National Semiconductor Corporation.

FACT is a trademark of Fairchild Semiconductor Corporation.

Pin Assignment for

DIP and SOIC

DS100232-1

Order Number LM1882CN or LM1882CM

For Default RS-170, Order Number

LM1882-RCN or LM1882-RCM

Pin Assignment

for LCC

DS100232-2

December 1998

LM1882

54ACT715

LM1882-R

54ACT715-R

Programmable

V

ideo

Sync

Generator

1998 National Semiconductor Corporation

DS100232

www.national.com

相關PDF資料 |

PDF描述 |

|---|---|

| 54ACT715P | SPECIALTY CONSUMER CIRCUIT, PDIP20 |

| 54ACT715S | SPECIALTY CONSUMER CIRCUIT, PDSO20 |

| LM1882CMX | SPECIALTY CONSUMER CIRCUIT, PDSO20 |

| LM1882-RD | SPECIALTY CONSUMER CIRCUIT, CDIP20 |

| 5962-9309701M2A | SPECIALTY CONSUMER CIRCUIT, CQCC20 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 54ACT723DM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x9 Asynchronous FIFO |

| 54ACT723FM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x9 Asynchronous FIFO |

| 54ACT723LM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x9 Asynchronous FIFO |

| 54ACT725DM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x9 Asynchronous FIFO |

| 54ACT725FM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x9 Asynchronous FIFO |

發布緊急采購,3分鐘左右您將得到回復。