- 您現在的位置:買賣IC網 > PDF目錄360456 > 74GTL1655TTR BUS TRANSCEIVER|DUAL|8-BIT|BICMOS|TSSOP|64PIN|PLASTIC PDF資料下載

參數資料

| 型號: | 74GTL1655TTR |

| 元件分類: | 通用總線功能 |

| 英文描述: | BUS TRANSCEIVER|DUAL|8-BIT|BICMOS|TSSOP|64PIN|PLASTIC |

| 中文描述: | 總線收發器|雙| 8位| BICMOS工藝| TSSOP封裝| 64管腳|塑料 |

| 文件頁數: | 1/14頁 |

| 文件大小: | 110K |

| 代理商: | 74GTL1655TTR |

1/14

December 2001

I

HIGH SPEED GTL/GTL+ UNIVERSAL

TRANSCEIVER :

t

PD

= 4.6 ns (MAX.) A to B at V

CC

= 3V

COMBINES D-TYPE LATCHES AND D-TYPE

FLIP-FLOPS FOR OPERATION IN

TRANSPARENT, LATCHED, OR CLOCKED

MODE

I

OPERATING VOLTAGE RANGE:

V

CC

(OPR) = 3.0V to 3.6V

I

SYMMETRICAL OUTPUT IMPEDANCE:

|I

OH

| = I

OL

=24mA (MIN) at V

CC

= 3V (A PORT)

I

OUTPUT IMPEDANCE:

I

OL

= 100mA (MIN) at V

CC

= 3V (B PORT)

HIGH-IMPEDANCE STATE DURING POWER

UP AND POWER DOWN up to Vcc=1.5V

PERMITT LIVE INSERTION

B-PORT PRECHARGED BY BIASVcc

REDUCE NOISE ON THE LINE DURING

LIVE INSERTION

EDGE RATE-CONTROL INPUT

CONFIGURES THE B-PORT OUTPUT RISE

AND FALL TIMES

BUS HOLD ON DATA INPUTS ELIMINATES

THE NEED FOR EXTERNAL PULL-UP/

PULL-DOWN RESISTORS (A PORT)

DISTRIBUTED VCC AND GND PIN

CONFIGURATION MINIMIZES HIGH-SPEED

SWITCHING NOISE IN PARALLEL

COMUNICATIONS .

I

PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 1655

I

I

I

I

I

I

DESCRIPTION

The 74GTL1655 devices are 16-bit high-drive

(100mA), low-output-impedance universal bus

transceivers designed for backplane applications.

The 74GTL1655 devices provide live-insertion

capability for backplane applications by tolerating

active signals on the data ports when the devices

are powered off. In addition, a biasing pin

preconditions the GTL/GTL+ port to minimize

disruption to an active backplane.

The edge rate-control (V

ERC

) input is provided so

the rise and fall time of the B outputs can be

configured to optimize for various backplane

loading conditions. Data flow in each direction is

controlled by output-enable (OEAB and OEBA),

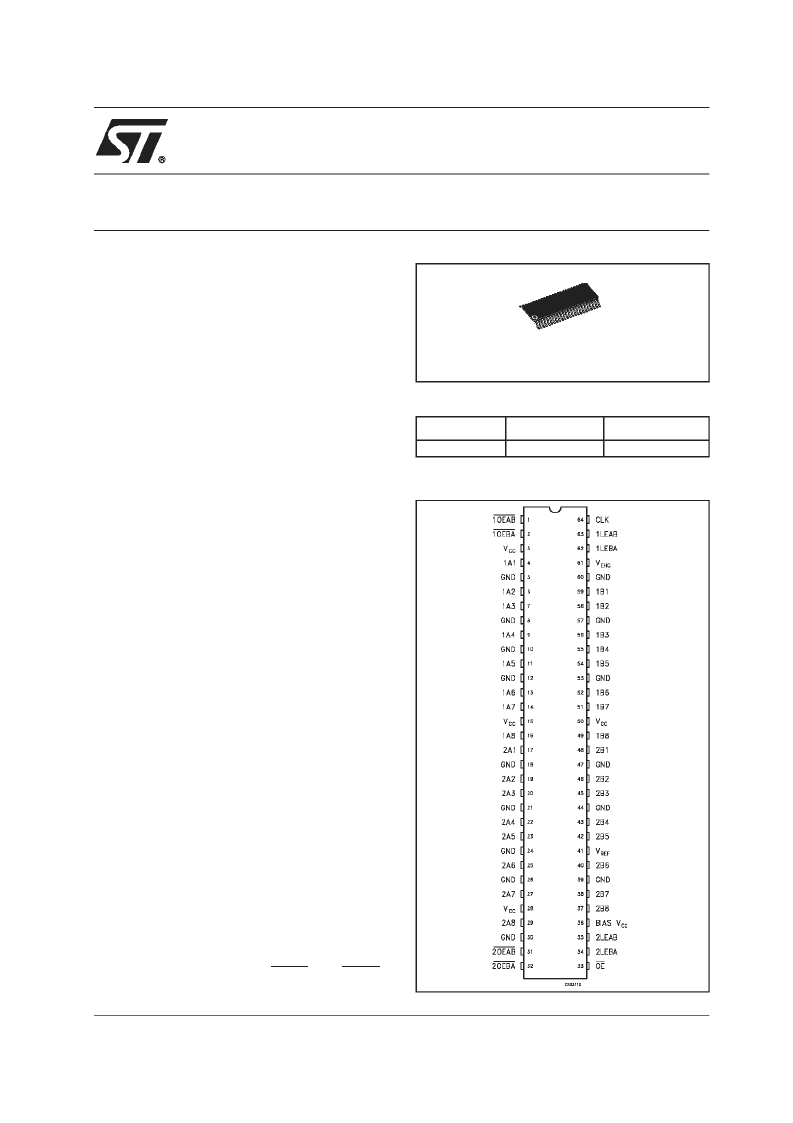

74GTL1655

16 BIT LVTTL TO GTL/GTL + UNIVERSAL BUS

TRANSCEIVERS WITH LIVE INSERTION

ORDER CODES

PACKAGE

TUBE

T & R

TSSOP

74GTL1655TTR

TSSOP

PIN CONNECTION

相關PDF資料 |

PDF描述 |

|---|---|

| 74H40DC | Dual 4-input NAND Gate |

| 74H40PC | Dual 4-input NAND Gate |

| 74H51PC | Dual 2/2-input AND-NOR Gate |

| 74H52PC | AND-OR Gate |

| 74H53DC | 2/2/2/3-input AND-NOR Gate |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 74GTL16612DGGRE4 | 功能描述:轉換 - 電壓電平 18B LVTTL-GTL/GTL Univ Bus Trans RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:MLF-8 |

| 74GTL16612DGGRG4 | 功能描述:轉換 - 電壓電平 18B LVTTL-to-GTL/GTL Univ Bus Xceivers RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:MLF-8 |

| 74GTL16616DGGRE4 | 功能描述:轉換 - 電壓電平 17B LVTTL-GTL/GTL Univ Bus Trans RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:MLF-8 |

| 74GTL16616DGGRG4 | 功能描述:轉換 - 電壓電平 17B LVTTL-To-GTL/GTL Univ Bus Xceivers RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:MLF-8 |

| 74GTL16622ADGGRE4 | 功能描述:轉換 - 電壓電平 18-Bit LVTTL To GTL/GTL+ Bus Trncvr RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:MLF-8 |

發布緊急采購,3分鐘左右您將得到回復。