- 您現在的位置:買賣IC網 > PDF目錄369351 > 78Q2120-64T (Electronic Theatre Controls, Inc.) 10/100BASE-TX Ethernet Transceiver PDF資料下載

參數資料

| 型號: | 78Q2120-64T |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 10/100BASE-TX Ethernet Transceiver |

| 中文描述: | 10/100BASE-TX以太網收發器 |

| 文件頁數: | 7/33頁 |

| 文件大小: | 200K |

| 代理商: | 78Q2120-64T |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

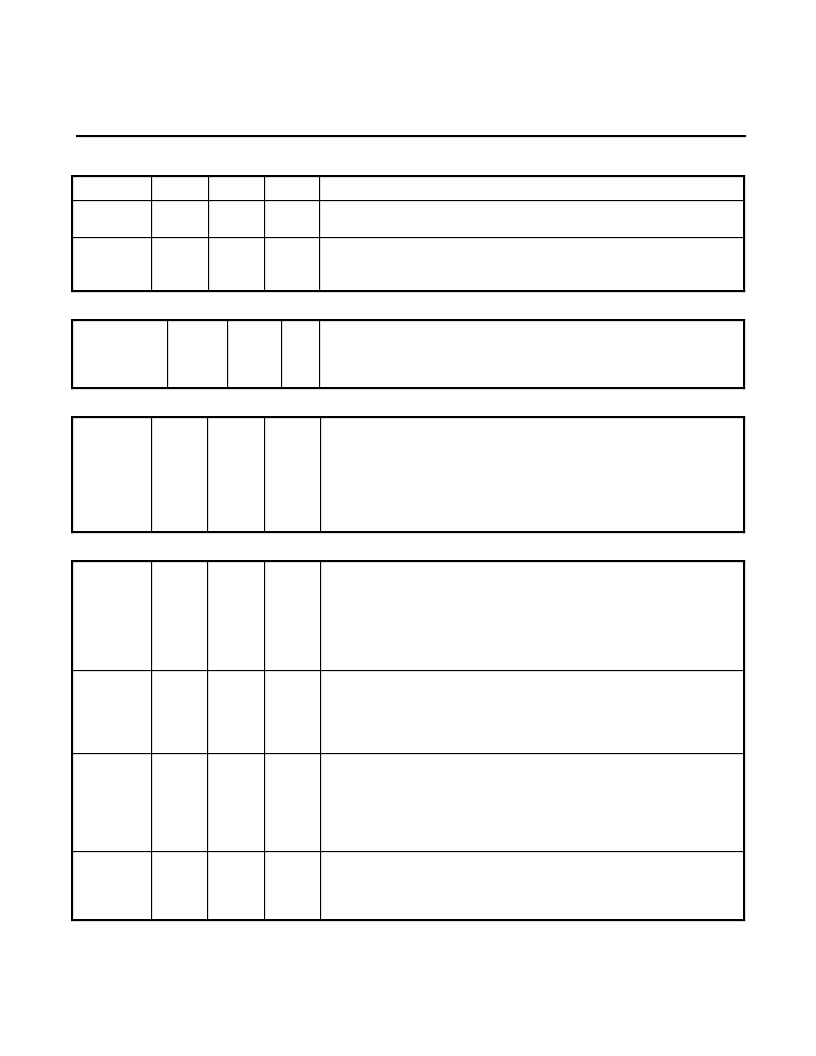

78Q2120

10/100BASE-TX

Ethernet Transceiver

MII

(continued)

7

PIN

64-PIN

80-PIN TYPE

DESCRIPTION

MDC

18

22

I

MANAGEMENT DATA CLOCK: MDC is the clock used for

transferring data via the MDIO pin.

MDIO

17

21

I/O

MANAGEMENT DATA INPUT/OUTPUT: MDIO is a bi-directional port

used to access management registers within the 78Q2120. This pin

requires an external pull-up resistor as specified in IEEE-802.3.

PHY ADDRESS

PHYAD[4:0]

12-16

14-18

I

PHY ADDRESS: Allows 31 configurable PHY addresses. The

78Q2120 always responds to data transactions via the MII interface

when the PHYAD bits are all zero independent of the logic levels of

the PHYAD pins.

PMA (PHYSICAL MEDIA ATTACHMENT) INTERFACE

PCSBP

64

1

I

PCS BYPASS: When high, the 100BASE-TX PCS is bypassed, as

well as the scrambler and descrambler functions. Scrambled 5bit

code groups for transmission are applied to the TX_ER, TXD[3:0]

pins and received on the RX_ER, RXD[3:0] pins. The RX_DV and

TX_EN signals are not valid in this mode. PCS bypass mode is only

valid when 100BASE-TX is enabled. This mode can also be entered

with MR16.1.

CONTROL AND STATUS

RST

6

8

I

RESET

: When pulled low the pin resets the chip. The reset pulse

must be long enough to guarantee stabilization of Vcc and startup

of the oscillator. There are 2 other ways to reset the chip:

i) through the internal power-on-reset (activated when the chip

is being powered up)

ii) through the MII register bit (MR 0.15)

PWRDN

7

9

I

POWER-DOWN: The 78Q2120 may be placed in a low power

consumption state by setting this signal to logic high. While in power-

down state, the 78Q2120 still responds to management transactions.

The same power-down state can also be achieved through the

PWRDN bit in the MII register (MR0.11).

ISO

2

3

I

ISOLATE: When set to logic one, the 78Q2120 will present a high

impedance on its MII output pins. This allows for multiple chips to be

attached to the same MII interface. When the 78Q2120 is isolated, it

still responds to management transactions. The same high

impedance state can also be achieved through the ISO bit in the MII

register (MR0.10).

ISODEF

1

2

I

ISOLATE DEFAULT: This pin determines the power-up/reset default

of the ISO bit (MR0.10). If it is connected to VDD (GND), ISO bit will

have a default value of 1 (0). When this signal is tied to VDD, it

allows multiple chips to be connected to the same MII interface.

相關PDF資料 |

PDF描述 |

|---|---|

| 78Q2120-CGT | 10/100BASE-TX Ethernet Transceiver |

| 78Q8392L | Low Power Ethernet Coaxial Transceiver |

| 78Q8392L-28CH | Low Power Ethernet Coaxial Transceiver |

| 78Q8392L-CP | Low Power Ethernet Coaxial Transceiver |

| 78S40 | RADIATION HARDENED HIGH EFFICIENCY, 5 AMP SWITCHING REGULATORS |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 78Q2120C | 制造商:TDK 制造商全稱:TDK Electronics 功能描述:10/100BASE - TX Transceiver |

| 78Q2120C09-64CGT | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:10/100BASE-TX Transceiver |

| 78Q2120C09-64CGT/F | 功能描述:以太網 IC 10-100 Fast Ethernet Transceiver RoHS:否 制造商:Micrel 產品:Ethernet Switches 收發器數量:2 數據速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| 78Q2120C09-64CGTR/F | 功能描述:TXRX 10/100 BASE 3.3V 64-LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 驅動器,接收器,收發器 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:25 系列:- 類型:收發器 驅動器/接收器數:2/2 規程:RS232 電源電壓:4.5 V ~ 5.5 V 安裝類型:通孔 封裝/外殼:16-DIP(0.300",7.62mm) 供應商設備封裝:16-PDIP 包裝:管件 |

| 78Q2120C09-CGTR/F | 功能描述:以太網 IC 10-100 Fast Ethernet Transceiver RoHS:否 制造商:Micrel 產品:Ethernet Switches 收發器數量:2 數據速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

發布緊急采購,3分鐘左右您將得到回復。