- 您現在的位置:買賣IC網 > PDF目錄24614 > 91305AGILFT (INTEGRATED DEVICE TECHNOLOGY INC) 91305 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 PDF資料下載

參數資料

| 型號: | 91305AGILFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 91305 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| 封裝: | 4.40 MM, 0.65 MM PITCH, LEAD FREE, MO-153, TSSOP-8 |

| 文件頁數: | 1/9頁 |

| 文件大小: | 157K |

| 代理商: | 91305AGILFT |

Integrated

Circuit

Systems, Inc.

General Description

Features

ICS91305I

0691E—08/20/04

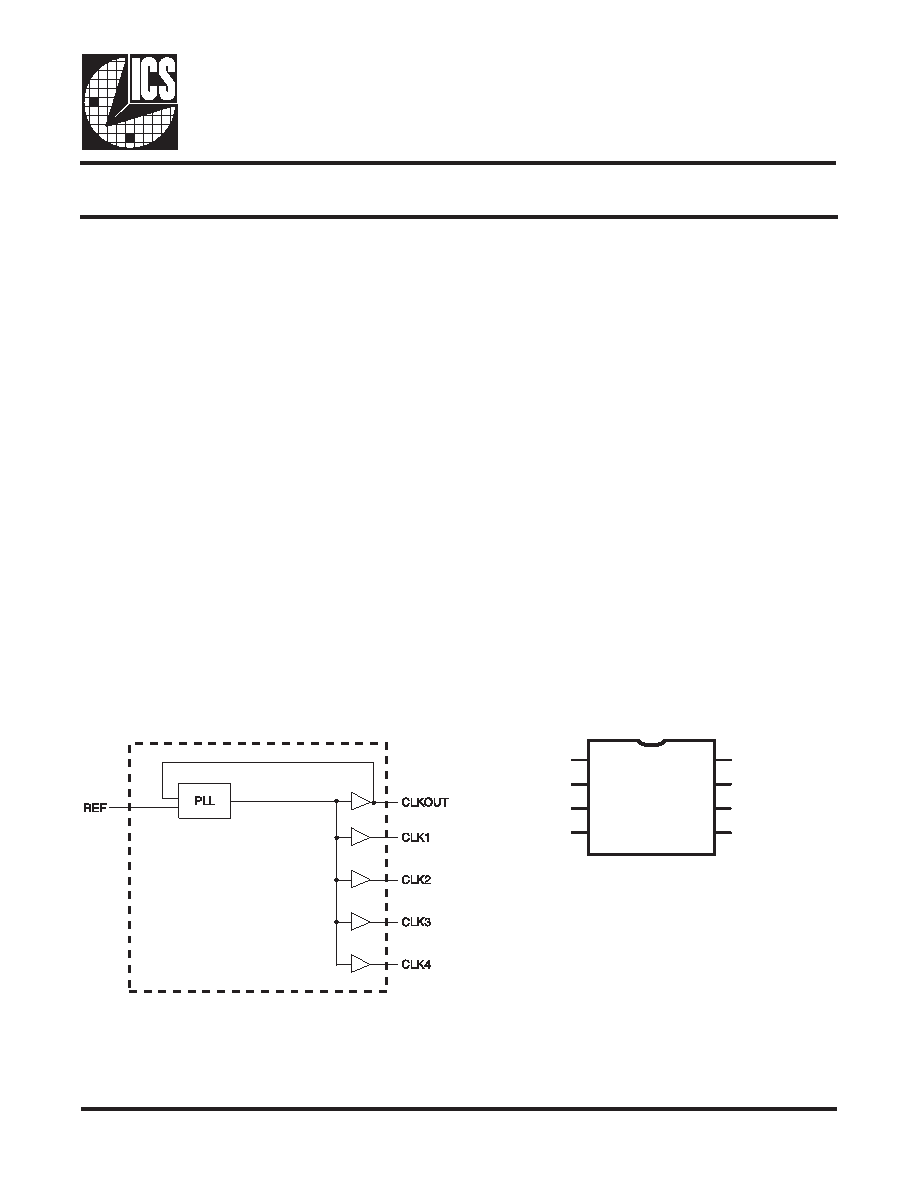

Block Diagram

High Performance Communication Buffer

Pin Configuration

Zero input - output delay

Frequency range 10 - 133 MHz (3.3V)

5V tolerant input REF

High loop filter bandwidth ideal for Spread

Spectrum applications.

Less than 200 ps Jitter between outputs

Skew controlled outputs

Skew less than 250 ps between outputs

Available in 8 pin 150 mil SOIC & 173 mil

TSSOP packages

3.3V ±10% operation

Supports industrial temperature range -40°C to

85°C

The ICS91305I is a high performance, low skew, low jitter

clock driver. It uses a phase lock loop (PLL) technology

to align, in both phase and frequency, the REF input with

the CLKOUT signal. It is designed to distribute high speed

clocks in communication systems operating at speeds

from 10 to 133 MHz.

ICS91305I is a zero delay buffer that provides

synchronization between the input and output. The

synchronization is established via CLKOUT feed back to

the input of the PLL. Since the skew between the input and

output is less than +/- 350 pS, the part acts as a zero delay

buffer.

The ICS91305I comes in an eight pin 150 mil SOIC

package. It has five output clocks. In the absence of REF

input, will be in the power down mode. In this mode, the

PLL is turned off and the output buffers are pulled low.

Power down mode provides the lowest power consumption

for a standby condition.

8 pin SOIC & TSSOP

REF

CLK2

CLK1

GND

CLKOUT

CLK4

VDD

CLK3

ICS913

05I

1

2

3

4

8

7

6

5

相關PDF資料 |

PDF描述 |

|---|---|

| 91305AMIT | 91305 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| 91305AMI | 91305 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| 91305AGLF | 91305 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| 91305AMLFT | 91305 SERIES, PLL BASED CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| 91305YGI-T | 91305 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 91305AGLF | 制造商:Integrated Device Technology Inc 功能描述:Zero Delay PLL Clock Buffer Single 10MHz to 133MHz 8-Pin TSSOP Tube 制造商:Integrated Device Technology Inc 功能描述:ZERO DLY PLL CLOCK BFFR SGL 10MHZ TO 133MHZ 8TSSOP - Rail/Tube |

| 91305AGLFT | 制造商:Integrated Device Technology Inc 功能描述:Zero Delay PLL Clock Buffer Single 10MHz to 133MHz 8-Pin TSSOP T/R 制造商:Integrated Device Technology Inc 功能描述:8 TSSOP (LEAD FREE) - Tape and Reel |

| 91305AMILF | 功能描述:時鐘驅動器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 91305AMILFT | 功能描述:時鐘驅動器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 91305AMLF | 功能描述:時鐘驅動器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

發布緊急采購,3分鐘左右您將得到回復。