- 您現在的位置:買賣IC網 > PDF目錄24624 > 9250BF-27 (INTEGRATED DEVICE TECHNOLOGY INC) 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF資料下載

參數資料

| 型號: | 9250BF-27 |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產生/分配 |

| 英文描述: | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 0.300 INCH, 0.025 INCH PITCH, MO-118, SSOP-56 |

| 文件頁數: | 1/17頁 |

| 文件大小: | 221K |

| 代理商: | 9250BF-27 |

Integrated

Circuit

Systems, Inc.

ICS9250-27

Third party brands and names are the property of their respective owners.

0395D—10/25/05

Recommended Application:

810/810E and 815 type chipset.

Output Features:

3 CPU (2.5V) (up to 133MHz achievable through I

2C)

9 SDRAM (3.3V) (up to 133MHz achievable

through I

2C)

7 PCI (3.3 V) @33.3MHz

2 IOAPIC (2.5V) @ 33.3 MHz

3 Hublink clocks (3.3 V) @ 66.6 MHz

2 (3.3V) @ 48 MHz (Non spread spectrum)

1 REF (3.3V) @ 14.318 MHz

Features:

Supports spread spectrum modulation,

0 to -0.5% down spread.

I

2C support for power management

Efficient power management scheme through PD#

Uses external 14.138 MHz crystal

Alternate frequency selections available through I

2C

control.

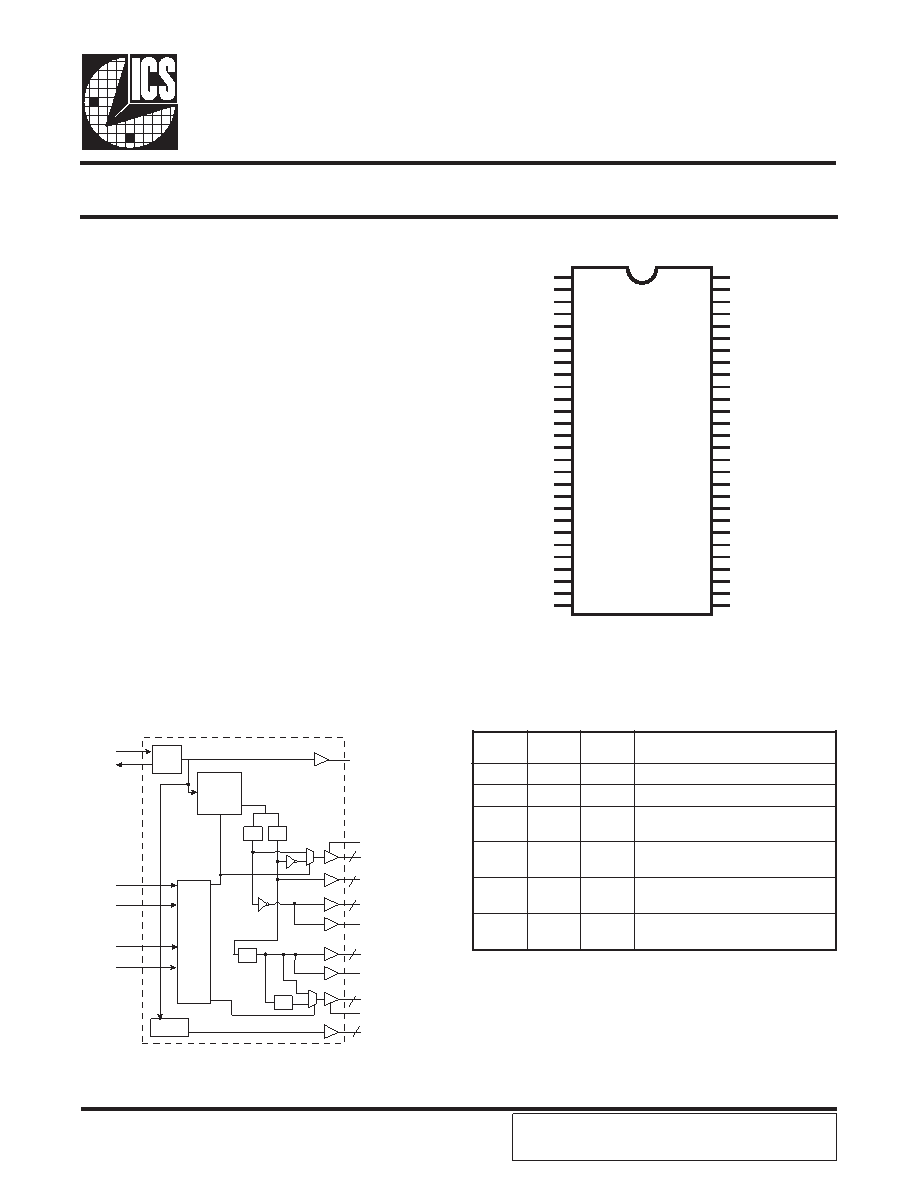

Functionality

Pin Configuration

56-Pin 300mil SSOP

* This input has a 50K

pull-down to GND.

*FS2//REF0

VDD

X1

X2

GND

3V66-0

3V66-1

3V66-2

VDD

PCICLK_F

PCICLK0

GND

PCICLK1

PCICLK2

GND

PCICLK3

PCICLK4

PCICLK5

VDD

GND

48MHz_0

48MHz_1

VDD

FS0

GND

IOAPIC0

IOAPIC1

VDDL

CPUCLK0

VDDL0

CPUCLK1

CPUCLK2

GNDL

GND

SDRAM0

SDRAM1

VDD

SDRAM2

SDRAM3

GND

SDRAM4

SDRAM5

VDD

SDRAM6

SDRAM7

GND

SDRAM_F

VDD

PD#

SCLK

SDATA

FS1

ICS9250-27

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

Frequency Generator & Integrated Buffers for Celeron & PII/III

2

S

F1

S

F0

S

Fn

o

i

t

c

n

u

F

X0

0

e

t

a

t

s

i

r

T

X0

1

t

s

e

T

01

0

z

H

M

6

=

U

P

C

e

v

i

t

c

A

z

H

M

0

1

=

M

A

R

D

S

01

1

z

H

M

0

1

=

U

P

C

e

v

i

t

c

A

z

H

M

0

1

=

M

A

R

D

S

11

0

z

H

M

3

1

=

U

P

C

e

v

i

t

c

A

z

H

M

3

1

=

M

A

R

D

S

11

1

z

H

M

3

1

=

U

P

C

e

v

i

t

c

A

z

H

M

0

1

=

M

A

R

D

S

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

REF0

CPU66/100/133 (2:0)

VDDL

3V66 (2:0)

SDRAM (7:0)

PCICLK (5:0)

IOAPIC (1:0)

VDDL

SDRAM_F

PCICLK_F

PLL2

48MHz (1:0)

X1

X2

XTAL

OSC

Control

Logic

Config

Reg

FS (2:0)

PD#

2

3

8

6

2

/2

/3

/2

PLL1

Spread

Spectrum

SDATA

SCLK

Power Groups

AVDD = Pin 22 Analog power for PLL

AGND = Pin 23 Analog ground

VDD48 = Pin 27 Analog power for 48MHz PLL

GND = Pin 24 Analog ground for 48MHz PLL

Block Diagram

相關PDF資料 |

PDF描述 |

|---|---|

| 9250BF-27LFT | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 051-928-9029 | RF Coaxial Connectors |

| 9250BF-28-T | 133.32 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 9250CF-10 | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 9250CF-10LF | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 9250BF27LF | 制造商:Integrated Device Technology Inc 功能描述:PLL Frequency Generator Dual 56-Pin SSOP Tube |

| 9250BF-27LF | 功能描述:時鐘發生器及支持產品 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| 9250BF-27LFT | 功能描述:時鐘發生器及支持產品 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| 9250BF-28LF | 制造商:Integrated Device Technology Inc 功能描述:PLL Frequency Generator Single 56-Pin SSOP Tube |

| 9250BF-28LFT | 制造商:Integrated Device Technology Inc 功能描述:PLL Frequency Generator Single 56-Pin SSOP T/R |

發布緊急采購,3分鐘左右您將得到回復。