- 您現在的位置:買賣IC網 > PDF目錄36336 > 935260348551 (NXP SEMICONDUCTORS) 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP44 PDF資料下載

參數資料

| 型號: | 935260348551 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | ADC |

| 英文描述: | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP44 |

| 封裝: | PLASTIC, SOT-307-2, QFP-44 |

| 文件頁數: | 2/24頁 |

| 文件大小: | 205K |

| 代理商: | 935260348551 |

1999 Jan 06

10

Philips Semiconductors

Preliminary specication

10-bit high-speed Analog-to-Digital

Converter (ADC)

TDA8765

Notes

1. The circuit has two clock inputs: CLK and CLK. There are four modes of operation:

a) PECL mode 1 (DC level varies equal to DC level of VCCD): CLK and CLK inputs are at differential PECL levels.

b) PECL mode 2 (DC level varies equal to DC level of VCCD): CLK input is at PECL level and sampling is taken on

the falling edge of the clock input signal. A DC level of 3.65 V has to be applied on CLK decoupled to GND via a

100 nF capacitor.

c) PECL mode 3 (DC level varies equal to DC level of VCCD): CLK input is at PECL level and sampling is taken on

the rising edge of the clock input signal. A DC level of 3.65 V has to be applied on CLK decoupled to GND via a

100 nF capacitor.

d) AC driving mode 4: when driving the CLK input directly and with any AC signal of minimum 0.5 V (p-p) and with

a DC level of 2.5 V, the sampling takes place at the falling edge of the clock signal.

When driving the CLK input with the same signal, sampling takes place at the rising edge of the clock signal. It is

recommended to decouple the CLK or CLK input to DGND via a 100 nF capacitor.

2. It is possible with an external reference connected to pin Vref to adjust the ADC input range. This voltage has to be

referenced to VCCA. For VCCA 1.825 V, the differential input voltage amplitude is 2 V (p-p).

3. The

3 dB analog bandwidth is determined by the 3 dB reduction in the reconstructed output, the input being a

full-scale sine wave.

4. THD (total harmonic distortion) is obtained with the addition of the first five harmonics:

where F is the fundamental harmonic referenced at 0 dB for a full-scale sine wave input.

5. Effective number of bits are obtained via a Fast Fourier Transform (FFT). The calculation takes into account all

harmonics and noise up to half of the clock frequency (Nyquist frequency). Conversion to SNR:

SNR = Nbit × 6.02 + 1.76 dB.

6. Intermodulation measured relative to either tone with analog input frequencies of 4.43 and 4.53 MHz. The two input

signals have the same amplitude and the total amplitude of both signals provides full-scale to the converter (

6dB

below full scale for each input signal).

d3 is the ratio of the RMS-value of either input tone to the RMS-value of the worst case third order intermodulation

product.

7. Output data acquisition: the output data is available after the maximum delay of td.

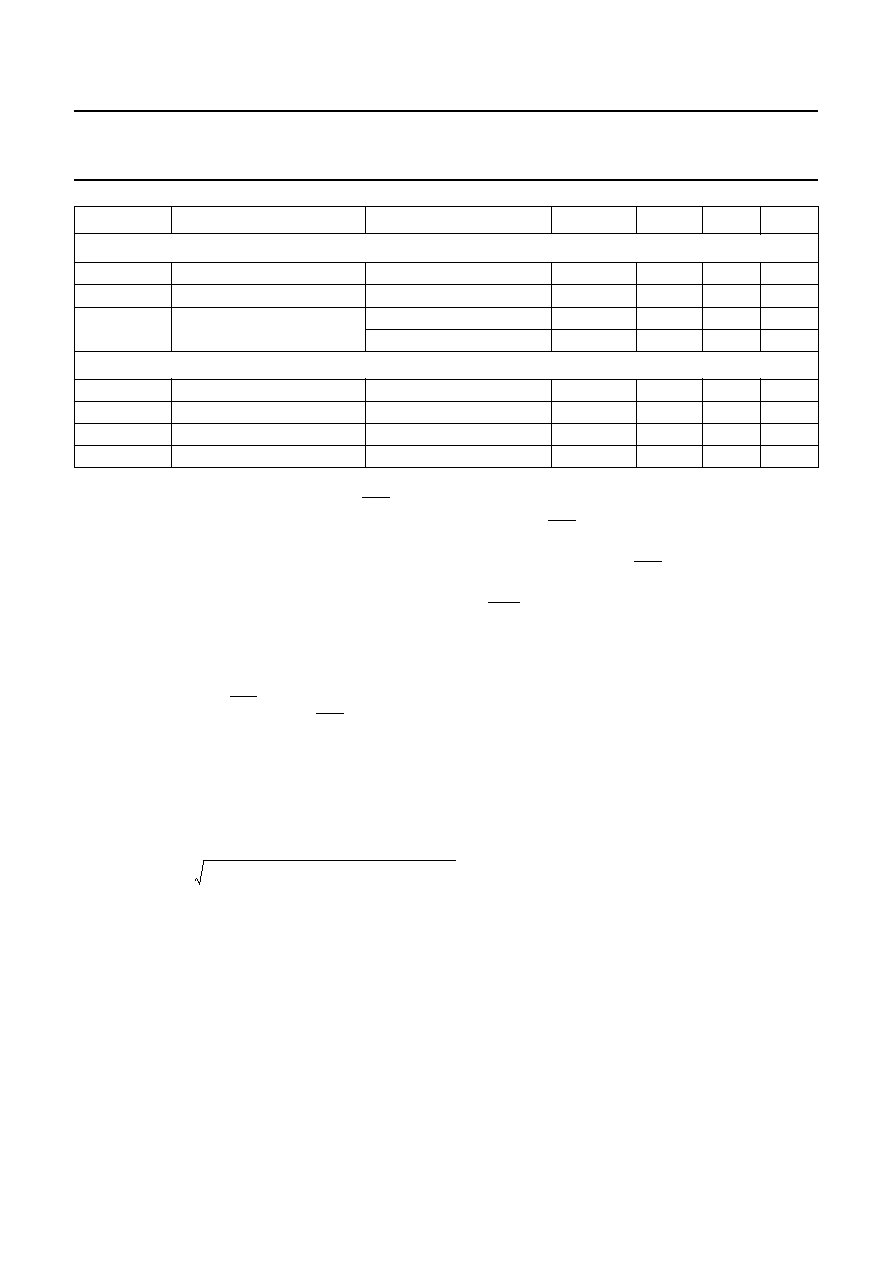

Timing (CL = 10 pF); see Fig.5 and note 7

td(s)

sampling delay time

2ns

th

output hold time

4

ns

td

output delay time

VCCO = 5.25 V

10

15

ns

VCCO = 3.0 V

13

18

ns

3-state output delay times; see Fig.6

tdZH

enable HIGH

14

18

ns

tdZL

enable LOW

16

20

ns

tdHZ

disable HIGH

16

20

ns

tdLZ

disable LOW

14

18

ns

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

THD

20 log

F

(2nd)

2

(3rd)

2

(4th)

2

(5th)

2

(6th)

2

+

+++

---------------------------------------------------------------------------------------------------------------

=

相關PDF資料 |

PDF描述 |

|---|---|

| 935260347518 | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP44 |

| 935260347551 | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP44 |

| 935260516551 | SPECIALTY ANALOG CIRCUIT, PQFP48 |

| 935260516557 | SPECIALTY ANALOG CIRCUIT, PQFP48 |

| 935250320551 | SPECIALTY ANALOG CIRCUIT, PQFP48 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 935261069122 | 制造商:NXP Semiconductors 功能描述:IC SECURITY TRANSPONDER PLLMC |

| 935262025112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935262217118 | 制造商:NXP Semiconductors 功能描述:Real Time Clock Serial 8-Pin SO T/R |

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

發布緊急采購,3分鐘左右您將得到回復。