- 您現在的位置:買賣IC網 > PDF目錄36337 > 935261242112 (NXP SEMICONDUCTORS) SERIAL INPUT LOADING, 20-BIT DAC, PDSO16 PDF資料下載

參數資料

| 型號: | 935261242112 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | DAC |

| 英文描述: | SERIAL INPUT LOADING, 20-BIT DAC, PDSO16 |

| 封裝: | 4.40 MM, PLASTIC, SSOP-16 |

| 文件頁數: | 18/21頁 |

| 文件大小: | 142K |

| 代理商: | 935261242112 |

2000 Jan 10

6

Philips Semiconductors

Preliminary specication

Low-cost stereo lter DAC

UDA1320ATS

8.3

Multiple format input interface

L3 mode:

I2S-bus with data word length of up to 20 bits

MSB-justified format with data word length up to 20 bits

LSB-justified format with data word length of 16,

18 or 20 bits.

8.4

Static pin mode

The UDA1320ATS/N2 supports the following data input

name formats in the static pin mode (via SF0 and SF1):

I2S bus with data word length of up to 20 bits

LSB-justified format with data word length of 16,

18 or 20 bits.

See Table 2, for the static pin codes of the 4 formats,

selectable via SF0 and SF1.

The UDA1320ATS/N2 also accepts double speed data for

double speed data monitoring purposes.

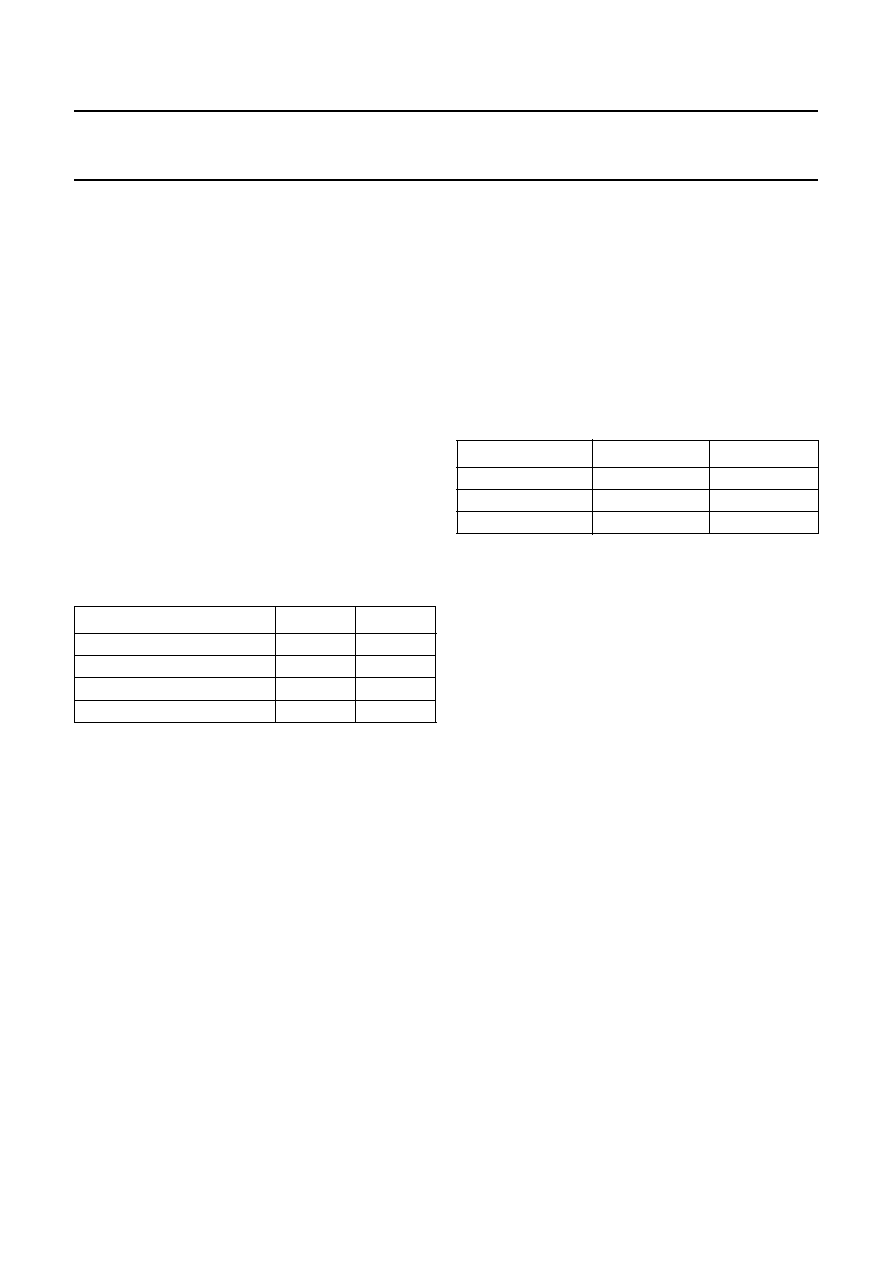

Table 2

Input format selection using SF0 and SF1

The formats are illustrated in Fig.3. Left and right

data-channel words are time multiplexed. The WS signal

must have 50% duty-factor for all LSB-justified modes.

For BCK and WS holds that the BCK frequency must be

equal or smaller then 64 times WS, or fBCK =< 64*fWS in

both L3 and static mode.

8.5

Pin compatibility

In L3 interface mode the UDA1320ATS/N2 can be used on

boards that are designed for the UDA1322. The software

for UDA1322 can be used for the UDA1320ATS/N2 to

control de-emphasis, volume control and mute and also

the status settings like system clock setting and input data

format.

IMPORTANT: UDA1320ATS/N2 differs from the

UDA1320TZ/N1 with respect to:

in the static mode 384fs is supported instead of 512fs.

the output voltage of the DAC. In the UDA1320TZ/N1

this is 800mVrms at 3.0V, now it is 1Vrms at 3.3V power

supply

8.6

Interpolation lter (DAC)

The digital filter interpolates from 1 to 128fs by cascading

a recursive filter and a FIR filter, see Table 3.

Table 3

Interpolation lter characteristics

8.7

Noise shaper

The 3rd-order noise shaper operates at 128fs. It shifts

in-band quantization noise to frequencies well above the

audio band. This noise shaping technique enables high

signal-to-noise ratios to be achieved. The noise shaper

output is converted into an analog signal using a

Filter-Stream DAC (FSDAC).

8.8

Filter-Stream DAC

The FSDAC is a semi-digital reconstruction filter that

converts the 1-bit data stream of the noise shaper to be

analog output voltage. The filter coefficients are

implemented as current sources and are summed at

virtual ground of the output operational amplifier. In this

way very high signal-to-noise performance and low clock

jitter sensitivity is achieved. A post-filter is not needed due

to the inherent filter function of the DAC. On-board

amplifiers convert the FSDAC output current to an output

voltage signal capable of driving a line output.

The output voltage of the FSDAC scales linearly with the

power supply voltage.

FORMAT

SF0

SF1

I2S0

0

LSB-justied 16 bits

0

1

LSB-justied 18 bits

1

0

LSB-justied 20 bits

1

ITEM

CONDITION

VALUE (dB)

Pass-band ripple

0 to 0.45fs

±0.1

Stop band

>0.55fs

50

Dynamic range

0 to 0.45fs

108

相關PDF資料 |

PDF描述 |

|---|---|

| 935261315112 | 2 CHANNEL(S), VOLUME CONTROL CIRCUIT, PDSO20 |

| 935261315118 | 2 CHANNEL(S), VOLUME CONTROL CIRCUIT, PDSO20 |

| 935261316112 | 2 CHANNEL(S), VOLUME CONTROL CIRCUIT, PDSO20 |

| 935261316118 | 2 CHANNEL(S), VOLUME CONTROL CIRCUIT, PDSO20 |

| 935261327518 | DUAL 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP64 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 935262025112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935262217118 | 制造商:NXP Semiconductors 功能描述:Real Time Clock Serial 8-Pin SO T/R |

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

發布緊急采購,3分鐘左右您將得到回復。