- 您現在的位置:買賣IC網 > PDF目錄25526 > 95V857AG-130T-LF (INTEGRATED DEVICE TECHNOLOGY INC) 95V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 PDF資料下載

參數資料

| 型號: | 95V857AG-130T-LF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 95V SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, MO-153, TSSOP-48 |

| 文件頁數: | 1/13頁 |

| 文件大小: | 138K |

| 代理商: | 95V857AG-130T-LF |

Integrated

Circuit

Systems, Inc.

ICS95V857 -XXX

0674R—12/15/04

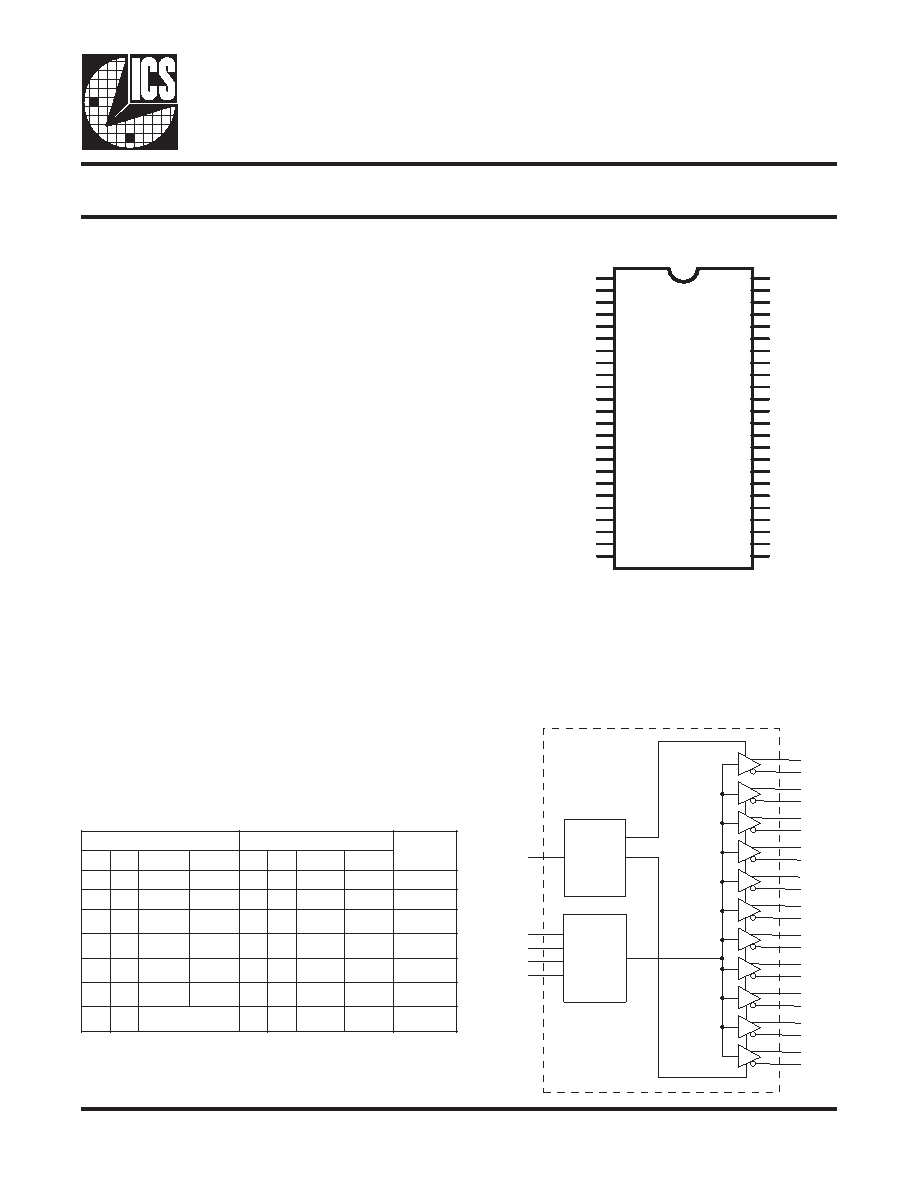

Block Diagram

2.5V Wide Range Frequency Clock Driver (45MHz - 233MHz)

Pin Configuration

48-Pin TSSOP/TVSOP

Recommended Application:

DDR Memory Modules / Zero Delay Board Fan Out

Provides complete DDR registered DIMM solution

with ICSSSTVF16857, ICSSSTVF16859 or

ICSSSTV32852

Product Description/Features:

Low skew, low jitter PLL clock driver

1 to 10 differential clock distribution (SSTL_2)

Feedback pins for input to output synchronization

PD# for power management

Spread Spectrum-tolerant inputs

Auto PD when input signal removed

Choice of static phase offset available,

for easy board tuning;

-XXX = device pattern number for options listed

below.

- ICS95V857 ............. 0ps

- ICS95V857-130 .. +50ps

Specifications:

Meets PC3200 Class A+ specification for DDR-I 400

support

Covers all DDRI speed grades

Switching Characteristics:

CYCLE - CYCLE jitter: <50ps

OUTPUT - OUTPUT skew: <40ps

Period jitter: ±30ps

S

T

U

P

N

IS

T

U

P

T

U

O

e

t

a

t

S

L

P

D

V

A#

D

PT

N

I

_

K

L

CC

N

I

_

K

L

CT

K

L

CC

K

L

CT

T

U

O

_

B

FC

T

U

O

_

B

F

D

N

GH

L

H

L

H

L

H

f

o

/

d

e

s

a

p

y

B

D

N

GH

H

L

H

L

H

L

f

o

/

d

e

s

a

p

y

B

V

5

.

2

)

m

o

n

(

LL

H

Z

f

o

V

5

.

2

)

m

o

n

(

LH

LZ

Z

f

o

V

5

.

2

)

m

o

n

(

HL

H

L

H

n

o

V

5

.

2

)

m

o

n

(

HH

L

H

L

H

L

n

o

V

5

.

2

)

m

o

n

(

X)

z

H

M

0

2

<

)

1

(

ZZ

Z

f

o

Functionality

PLL

FB_INT

FB_INC

CLK_INC

CLK_INT

PD#

Control

Logic

FB_OUTT

FB_OUTC

CLKT0

CLKT1

CLKT2

CLKT3

CLKT4

CLKT5

CLKT6

CLKT7

CLKT8

CLKT9

CLKC0

CLKC1

CLKC2

CLKC3

CLKC4

CLKC5

CLKC6

CLKC7

CLKC8

CLKC9

6.10 mm Body, 0.50 mm Pitch = TSSOP

4.40 mm Body, 0.40 mm Pitch = TVSOP

GND

CLKC0

CLKT0

VDD

CLKT1

CLKC1

GND

CLKC2

CLKT2

VDD

CLK_INT

CLK_INC

VDD

AVDD

AGND

GND

CLKC3

CLKT3

VDD

CLKT4

CLKC4

GND

CLKC5

CLKT5

VDD

CLKT6

CLKC6

GND

CLKC7

CLKT7

VDD

PD#

FB_INT

FB_INC

VDD

FB_OUTC

FB_OUTT

GND

CLKC8

CLKT8

VDD

CLKT9

CLKC9

GND

ICS

9

5V857-XXX

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

相關PDF資料 |

PDF描述 |

|---|---|

| 95V857AGILF-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 95V857ALILF-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 95V857AKI-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC40 |

| 95V857AKILF-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), QCC40 |

| 95V857AGI-T | PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 95V857AGILF | 功能描述:時鐘驅動器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 95V857AGILFT | 功能描述:時鐘驅動器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 95V857AGLF | 功能描述:時鐘驅動器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 95V857AGLFT | 功能描述:時鐘驅動器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 95V857AGLN | 制造商:Integrated Device Technology Inc 功能描述:48 TSSOP - Rail/Tube |

發布緊急采購,3分鐘左右您將得到回復。