- 您現在的位置:買賣IC網 > PDF目錄25548 > 97U877YKLF-T (INTEGRATED DEVICE TECHNOLOGY INC) 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 PDF資料下載

參數資料

| 型號: | 97U877YKLF-T |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 |

| 封裝: | LEAD FREE, PLASTIC, MLF-40 |

| 文件頁數: | 1/13頁 |

| 文件大小: | 640K |

| 代理商: | 97U877YKLF-T |

Integrated

Circuit

Systems, Inc.

ICS97U877

0792A—04/15/04

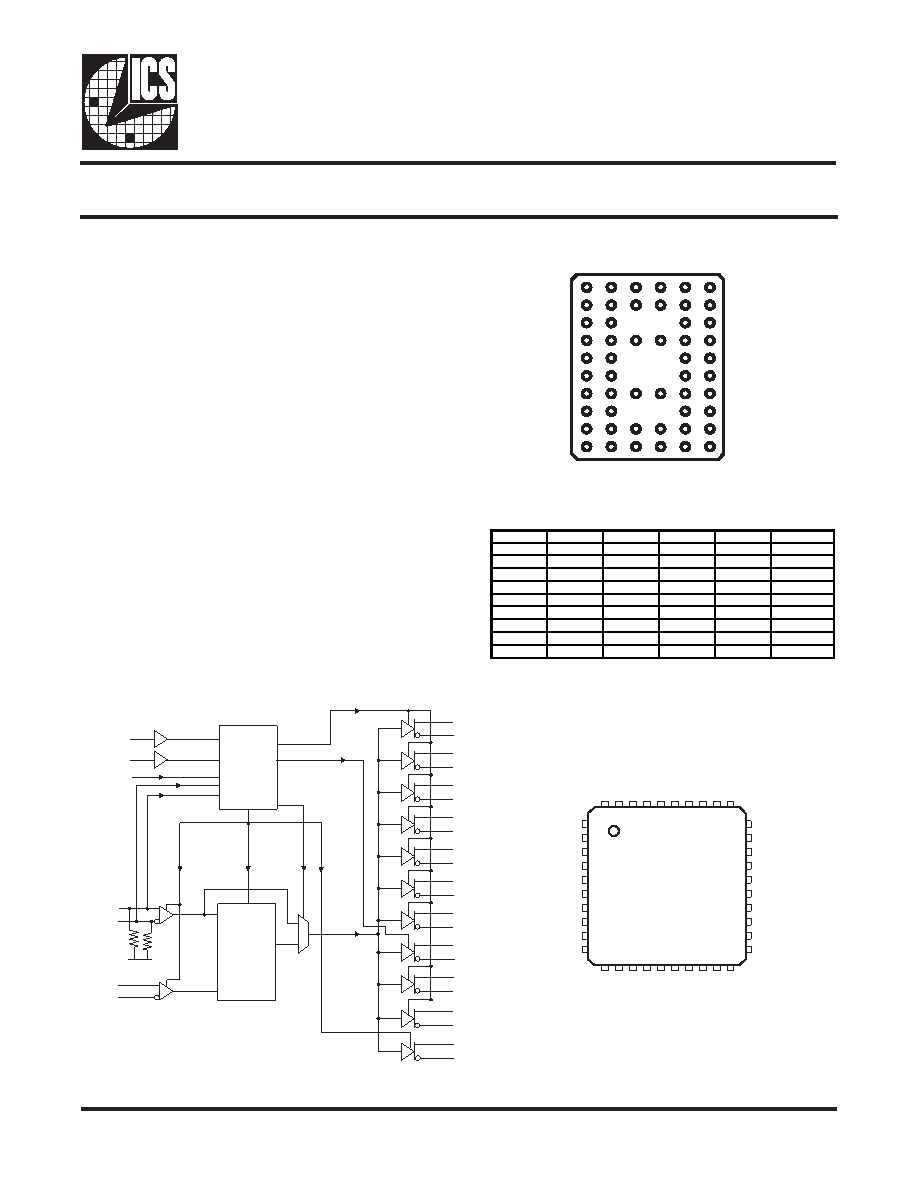

Block Diagram

1.8V Wide Range Frequency Clock Driver

Pin Configuration

40-Pin MLF

Recommended Application:

DDR2 Memory Modules / Zero Delay Board Fan Out

Provides complete DDR DIMM logic solution with

ICSSSTU32864

Product Description/Features:

Low skew, low jitter PLL clock driver

1 to 10 differential clock distribution (SSTL_18)

Feedback pins for input to output synchronization

Spread Spectrum tolerant inputs

Auto PD when input signal is at a certain logic state

Switching Characteristics:

Period jitter: 40ps

Half-period jitter: 60ps

CYCLE - CYCLE jitter 40ps

OUTPUT - OUTPUT skew: 40ps

A

B

123456

C

D

E

F

G

H

J

K

VDDQ

CLKC2

CLKT2

CLK_INT

CLK_INC

VDDQ

AGND

AVDD

VDDQ

GND

CLKC7

CLKT7

VDDQ

FB_INT

FB_INC

FB_OUTC

FB_OUTT

VDDQ

OE

OS

CLKT3

CLKC3

CLKC4

CLKT4

VDDQ

CLKT9

CLKC9

CLKC8

CLKT8

VDDQ

CLKC1

CLKT1

CLKT0

CLKC0

VDDQ

CLKC5

CLKT5

CLKT6

CLKC6

VDDQ

1

10

11

20

21

31

30

40

ICS97U877

52-Ball BGA

Top View

CLKT0

CLKC0

CLKT1

CLKC1

CLKT2

CLKC2

CLKT3

CLKC3

CLKT4

CLKC4

CLKT5

CLKC5

CLKT6

CLKC6

CLKT7

CLKC7

CLKT8

CLKC8

CLKT9

CLKC9

FB_OUTT

FB_OUTC

AV

DD

FB_INT

CLK_INT

CLK_INC

FB_INC

PLL

Powerdown

Control and

Test Logic

OE

LD* or OE

PLL bypass

LD*

LD*, OS or OE

OS

GND

10K-100k

* The Logic Detect (LD) powers down the device when a

logic low is applied to both CLK_INT and CLK_INC.

12345

6

A

CLKT1

CLKT0

CLKC0

CLKC5

CLKT5

CLKT6

B

CLKC1

GND

CLKC6

C

CLKC2

GND

NB

GND

CLKC7

D

CLKT2

VDDQ

OS

CLKT7

E

CLK_INT

VDDQ

NB

VDDQ

FB_INT

F

CLK_INC

VDDQ

NB

OE

FB_INC

G

AGND

VDDQ

FB_OUTC

H

AVDD

GND

NB

GND

FB_OUTT

J

CLKT3

GND

CLKT8

K

CLKC3

CLKC4

CLKT4

CLKT9

CLKC9

CLKC8

相關PDF資料 |

PDF描述 |

|---|---|

| 97U877YHLF-T | 97U SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 97ULP877AHLF-T | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 97ULP877BHLF-T | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 97ULP877BHLF | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 97ULP877BKLF | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 97ULP844AH | 功能描述:時鐘驅動器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 97ULP844AHLF | 功能描述:時鐘驅動器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 97ULP844AHLFT | 功能描述:時鐘驅動器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 97ULP844AHT | 功能描述:時鐘驅動器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 97ULP845AH | 功能描述:時鐘驅動器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

發布緊急采購,3分鐘左右您將得到回復。