- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25564 > 9DB433AFILFT (INTEGRATED DEVICE TECHNOLOGY INC) 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 PDF資料下載

參數(shù)資料

| 型號: | 9DB433AFILFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 封裝: | 0.209 INCH, ROHS COMPLIANT, MO-150, SSOP-28 |

| 文件頁數(shù): | 1/16頁 |

| 文件大小: | 306K |

| 代理商: | 9DB433AFILFT |

9DB433

IDT

Four Output Differential Buffer for PCIe Gen 3

1658A - 06/30/10

Four Output Differential Buffer for PCIe Gen 3

DATASHEET

1

Output Features

4 - 0.7V current-mode differential HSCL output pairs.

Supports zero delay buffer mode and fanout mode

Selectable bandwidth

50-110 MHz operation in PLL mode

5-166 MHz operation in Bypass mode

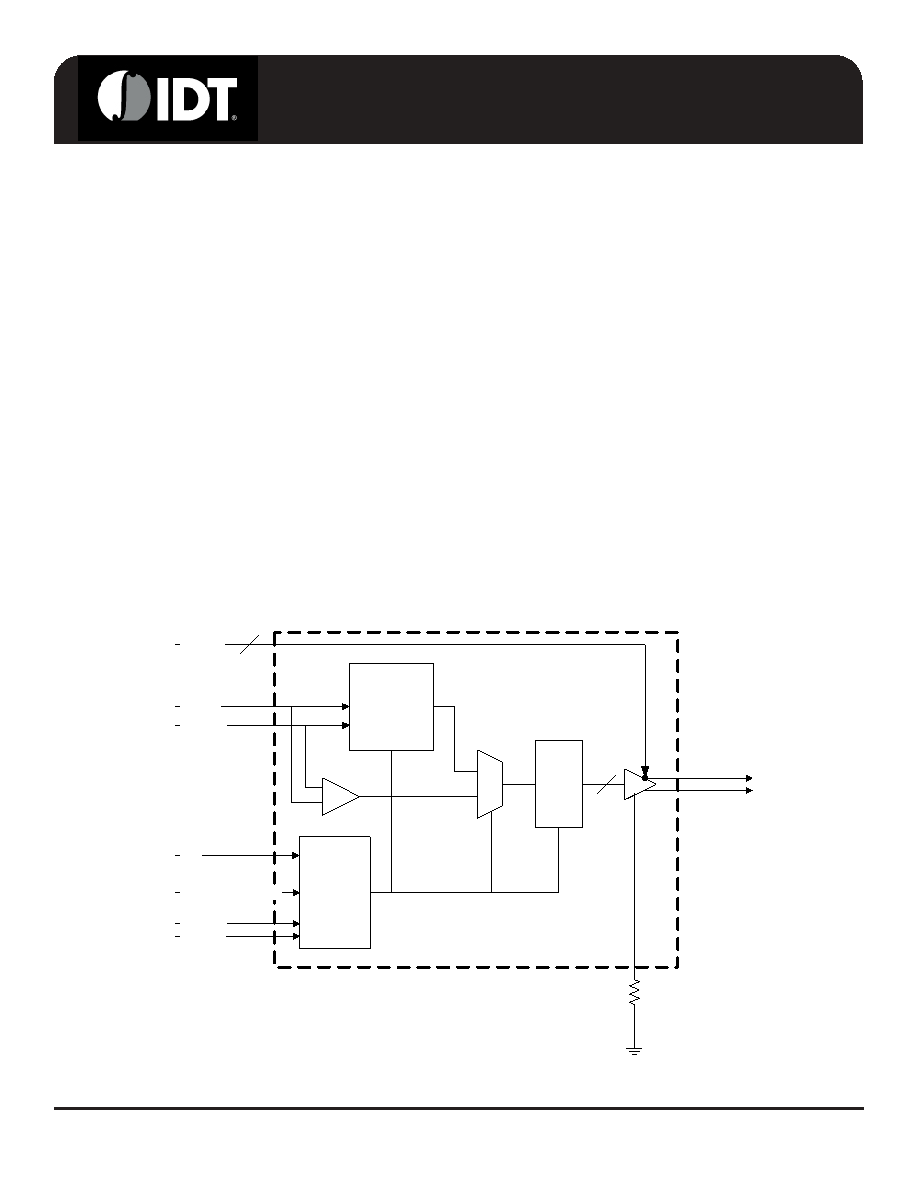

Functional Block Diagram

Key Specifications

Output cycle-cycle jitter < 50ps.

Output to Output skew <50ps

Phase jitter: PCIe Gen3 < 1.0ps rms

Features/Benefits

3 Selectable SMBus Addresses/Mulitple devices can share

the same SMBus Segment

OE# pins/Suitable for Express Card applications

PLL or bypass mode/PLL can dejitter incoming clock

Selectable PLL bandwidth/minimizes jitter peaking in

downstream PLL's

Spread Spectrum Compatible/tracks spreading input clock

for low EMI

SMBus Interface/unused outputs can be disabled

Supports undriven differential outputs in Power Down mode

for power management

Recommended Application:

4 output PCIe Gen3 zero-delay/fanout buffer

General Description:

The 9DB433 zero-delay buffer supports PCIe Gen3

requirements, while being backwards compatible to PCIe Gen2

and Gen1. The 9DB433 is driven by a differential SRC output

pair from an IDT 932S421 or 932SQ420 or equivalent main

clock generator.

STOP

LOGIC

SRC_IN

SRC_IN#

DIF(6,5,2,1)

CONTROL

LOGIC

BYP#_LOBW_HIBW

SMBDAT

SMBCLK

PD#

SPREAD

COMPATIBLE

PLL

4

IREF

M

U

X

OE(6,1)#

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9DB433AFLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB433AFLIFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB433AGILFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB433AFLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 9DB633AFLIFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9DB433AFLF | 功能描述:時鐘緩沖器 4 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB433AFLFT | 功能描述:時鐘緩沖器 4 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB433AGILF | 功能描述:時鐘緩沖器 4 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB433AGILFT | 功能描述:鎖相環(huán) - PLL 4 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| 9DB433AGLF | 功能描述:時鐘緩沖器 4 OUTPUT PCIE GEN3 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。