- 您現在的位置:買賣IC網 > PDF目錄25569 > 9LPR502YGLFT (INTEGRATED DEVICE TECHNOLOGY INC) SPECIALTY MICROPROCESSOR CIRCUIT, PDSO56 PDF資料下載

參數資料

| 型號: | 9LPR502YGLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO56 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-56 |

| 文件頁數: | 1/29頁 |

| 文件大小: | 282K |

| 代理商: | 9LPR502YGLFT |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

ICS9LPR502

IDTTM/ICSTM

56-pin CK505 w/Fully Integrated Voltage Regulator

1124D—02/26/09

56-PIN CK505 W/FULLY INTEGRATED VOLTAGE

REGULATOR

1

Datasheet

Recommended Application:

Key Specifications:

CK505 compliant clock with fully integrated voltage

regulator, PCIe Gen 1 compliant

CPU outputs cycle-cycle jitter < 85ps

SRC output cycle-cycle jitter < 125ps

PCI outputs cycle-cycle jitter < 250ps

+/- 100ppm frequency accuracy on CPU & SRC

clocks

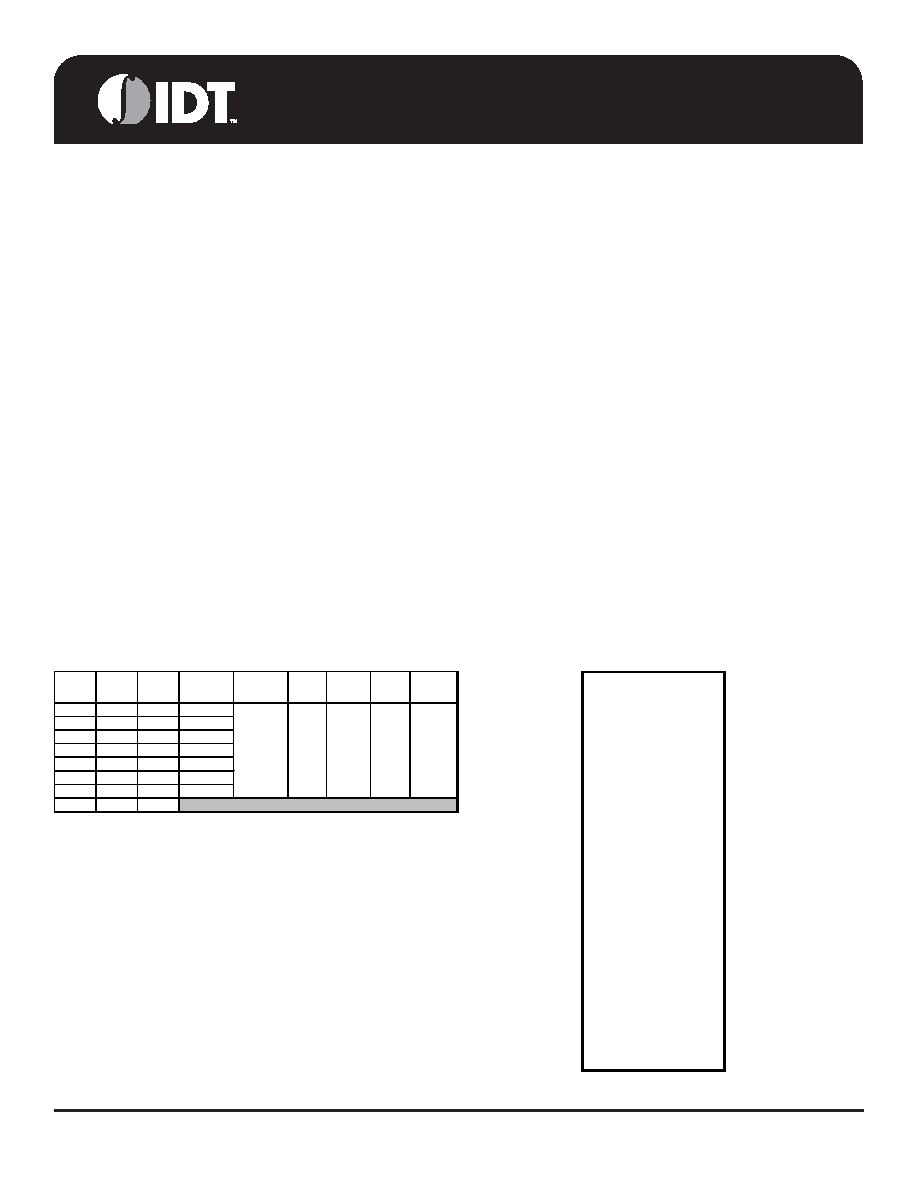

Pin Configuration

Output Features:

2 - CPU differential low power push-pull pairs

7 - SRC differential low power push-pull pairs

1 - CPU/SRC selectable differential low power push-pull

pair

1 - SRC/DOT selectable differential low power push-pull

pair

5 - PCI, 33MHz

1 - PCI_F, 33MHz free running

1 - USB, 48MHz

1 - REF, 14.318MHz

Features/Benefits:

Does not require external pass transistor for voltage

regulator

Supports spread spectrum modulation, default is 0.5%

down spread

Uses external 14.318MHz crystal, external crystal

load caps are required for frequency tuning

One differential push-pull pair selectable between

SRC and two single-ended outputs

Table 1: CPU Frequency Select Table

PCI0/CR#_A 1

56 SCLK

VDDPCI 2

55 SDATA

PCI1/CR#_B 3

54 REF0/FSLC/TEST_SEL

PCI2/TME 4

53 VDDREF

PCI3 5

52 X1

PCI4/SRC5_EN 6

51 X2

PCI_F5/ITP_EN 7

50 GNDREF

GNDPCI 8

49 FSLB/TEST_MODE

VDD48 9

48 CK_PWRGD/PD#

USB_48MHz/FSLA 10

47 VDDCPU

GND4811

46CPUT0

VDDI/O96Mhz 12

45 CPUC0

DOTT_96/SRCT0 13

44 GNDCPU

DOTC_96/SRCC0 14

43 CPUT1

GND 15

42 CPUC1

VDD 16

41 VDDI/OCPU

SRCT1/SE1 17

40 NC

SRCC1/SE218

39CPUT2_ITP/SRCT8

GND 19

38 CPUC2_ITP/SRCC8

VDDPLL3I/O 20

37 VDDSRCI/O

SRCT2/SATAT 21

36 SRCT7/CR#_F

SRCC2/SATAC 22

35 SRCC7/CR#_E

GNDSRC 23

34 GNDSRC

SRCT3/CR#_C 24

33 SRCT6

SRCC3/CR#_D 25

32 SRCC6

VDDSRCI/O 26

31 VDDSRC

SRCT4 27

30 PCI_STOP#/SRCT5

SRCC4 28

29 CPU_STOP#/SRCC5

56-SSOP/TSSOP

IC

S

9

L

PR

5

0

2

FSLC

2

B0b7

FSLB

1

B0b6

FSLA

1

B0b5

CPU

MHz

SRC

MHz

PCI

MHz

REF

MHz

USB

MHz

DOT

MHz

0

266.66

0

1

133.33

0

1

0

200.00

0

1

166.66

1

0

333.33

1

0

1

100.00

1

0

400.00

11

1

1. FS

LA and FSLB are low-threshold inputs.Please see VIL_FS and VIH_FS specifications in

the Input/Supply/Common Output Parameters Table for correct values.

Also refer to the Test Clarification Table.

2. FS

LC is a three-level input. Please see the VIL_FS and VIH_FS

specifications in the Input/Supply/Common Output Parameters Table for correct values.

Reserved

100.00

33.33

14.318

48.00

96.00

相關PDF資料 |

PDF描述 |

|---|---|

| 9LPRS365BKLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC64 |

| 9LPRS365BGLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO64 |

| 9LPRS436CKLF | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC48 |

| 9LPRS436CGLF | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 |

| 9LPRS436CKLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC48 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 9LPR502YKLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:56-PIN CK505 W/FULLY INTEGRATED VOLTAGE REGULATOR |

| 9LPR515CGLF | 功能描述:IC CLOCK MANANGEMENT 制造商:idt, integrated device technology inc 系列:* 零件狀態:最後搶購 標準包裝:1 |

| 9LPR515CGLFT | 功能描述:IC CLOCK MANANGEMENT 制造商:idt, integrated device technology inc 系列:* 零件狀態:最後搶購 標準包裝:1,000 |

| 9LPR515CKLF | 功能描述:IC CLOCK MANANGEMENT 制造商:idt, integrated device technology inc 系列:* 零件狀態:最後搶購 標準包裝:1 |

| 9LPR515CKLFT | 功能描述:IC CLOCK MANANGEMENT 制造商:idt, integrated device technology inc 系列:* 零件狀態:最後搶購 標準包裝:1,000 |

發布緊急采購,3分鐘左右您將得到回復。