參數資料

| 型號: | A3PE600-PQG208I |

| 廠商: | Microsemi SoC |

| 文件頁數: | 1/162頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 600000 GATES 208-PQFP |

| 標準包裝: | 24 |

| 系列: | ProASIC3E |

| RAM 位總計: | 110592 |

| 輸入/輸出數: | 147 |

| 門數: | 600000 |

| 電源電壓: | 1.425 V ~ 1.575 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應商設備封裝: | 208-PQFP(28x28) |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁

January 2013

I

2013 Microsemi Corporation

ProASIC3E Flash Family FPGAs

with Optional Soft ARM Support

Features and Benefits

High Capacity

600 k to 3 Million System Gates

108 to 504 kbits of True Dual-Port SRAM

Up to 620 User I/Os

Reprogrammable Flash Technology

130-nm, 7-Layer Metal (6 Copper), Flash-Based CMOS

Process

Instant On Level 0 Support

Single-Chip Solution

Retains Programmed Design when Powered Off

On-Chip User Nonvolatile Memory

1 kbit of FlashROM with Synchronous Interfacing

High Performance

350 MHz System Performance

3.3 V, 66 MHz 64-Bit PCI

In-System Programming (ISP) and Security

ISP Using On-Chip 128-Bit Advanced Encryption Standard

(AES) Decryption via JTAG (IEEE 1532–compliant)

FlashLock Designed to Secure FPGA Contents

Low Power

Core Voltage for Low Power

Support for 1.5-V-Only Systems

Low-Impedance Flash Switches

High-Performance Routing Hierarchy

Segmented, Hierarchical Routing and Clock Structure

Ultra-Fast Local and Long-Line Network

Enhanced High-Speed, Very-Long-Line Network

High-Performance, Low-Skew Global Network

Architecture Supports Ultra-High Utilization

Pro (Professional) I/O

700 Mbps DDR, LVDS-Capable I/Os

1.5 V, 1.8 V, 2.5 V, and 3.3 V Mixed-Voltage Operation

Bank-Selectable I/O Voltages—up to 8 Banks per Chip

Single-Ended

I/O

Standards:

LVTTL,

LVCMOS

3.3 V /

2.5 V / 1.8 V / 1.5 V, 3.3 V PCI / 3.3 V PCI-X, and LVCMOS

2.5 V / 5.0 V Input

Differential I/O Standards: LVPECL, LVDS, B-LVDS, and

M-LVDS

Voltage-Referenced I/O Standards: GTL+ 2.5 V / 3.3 V, GTL

2.5 V / 3.3 V, HSTL Class I and II, SSTL2 Class I and II, SSTL3

Class I and II

I/O Registers on Input, Output, and Enable Paths

Hot-Swappable and Cold Sparing I/Os

Programmable Output Slew Rate and Drive Strength

Programmable Input Delay

Schmitt Trigger Option on Single-Ended Inputs

Weak Pull-Up/-Down

IEEE 1149.1 (JTAG) Boundary Scan Test

Pin-Compatible Packages across the ProASIC3E Family

Clock Conditioning Circuit (CCC) and PLL

Six CCC Blocks, Each with an Integrated PLL

Configurable Phase-Shift, Multiply/Divide, Delay Capabilities

and External Feedback

Wide Input Frequency Range (1.5 MHz to 350 MHz)

SRAMs and FIFOs

Variable-Aspect-Ratio 4,608-Bit RAM Blocks (×1, ×2, ×4, ×9,

and ×18 organizations available)

True Dual-Port SRAM (except ×18)

24 SRAM and FIFO Configurations with Synchronous Operation

up to 350 MHz

ARM Processor Support in ProASIC3E FPGAs

M1 ProASIC3E Devices—Cortex-M1 Soft Processor Available

with or without Debug

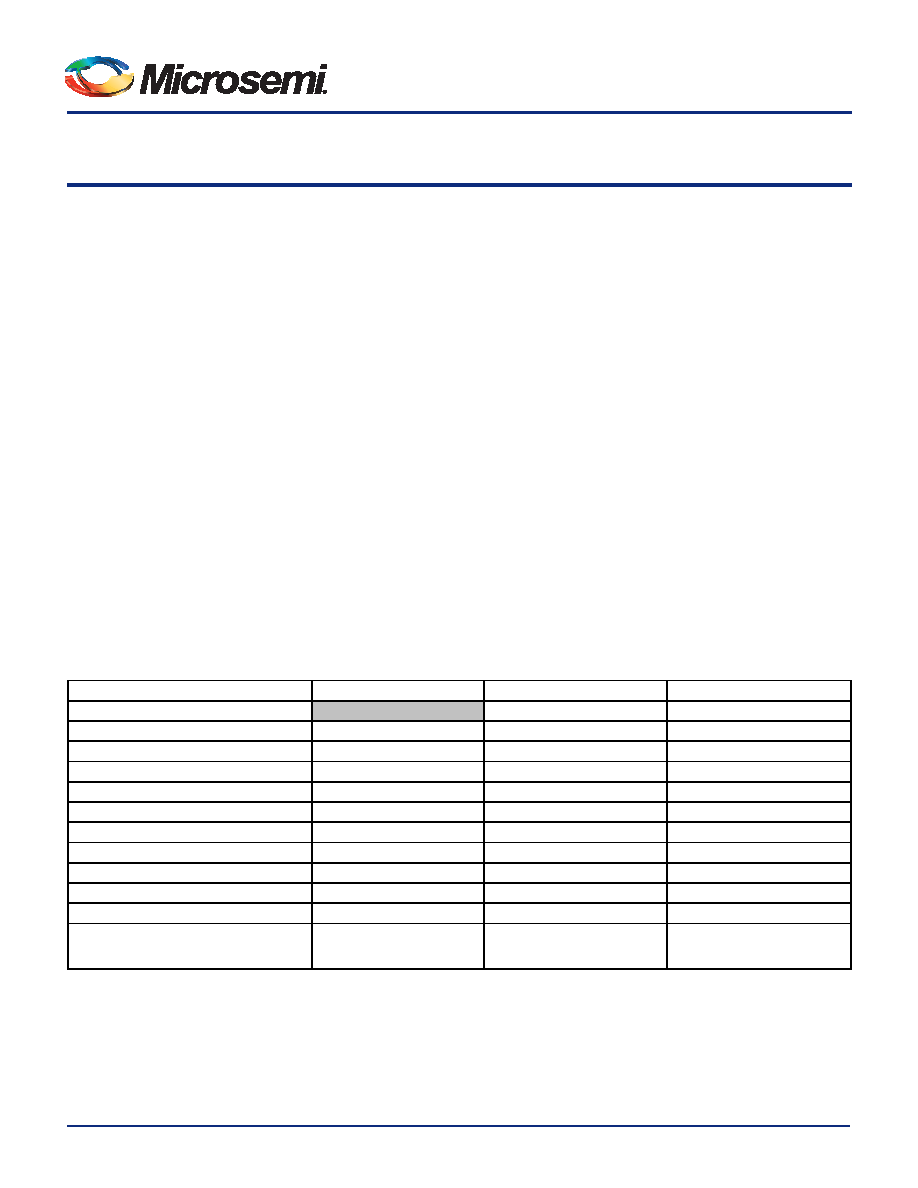

Table 1-1 ProASIC3E Product Family

ProASIC3E Devices

A3PE600

A3PE1500

A3PE3000

Cortex-M1 Devices 1

M1A3PE1500

M1A3PE3000

System Gates

600,000

1,500,000

3,000,000

VersaTiles (D-flip-flops)

13,824

38,400

75,264

RAM Kbits (1,024 bits)

108

270

504

4,608-Bit Blocks

24

60

112

FlashROM Kbits

11

1

Secure (AES) ISP

Yes

CCCs with Integrated PLLs2

66

6

VersaNet Globals3

18

I/O Banks

88

8

Maximum User I/Os

270

444

620

Package Pins

PQFP

FBGA

PQ208

FG256, FG484

PQ208

FG484, FG676

PQ208

FG324

, FG484, FG896

Notes:

1. Refer to the Cortex-M1 product brief for more information.

2. The PQ208 package supports six CCCs and two PLLs.

3. Six chip (main) and three quadrant global networks are available.

4. For devices supporting lower densities, refer to the ProASIC3 Flash Family FPGAs datasheet.

Revision 13

相關PDF資料 |

PDF描述 |

|---|---|

| ACM43DRMN-S288 | CONN EDGECARD EXTEND 86POS 0.156 |

| A54SX08-PQG208 | IC FPGA SX 12K GATES 208-PQFP |

| ACM43DRMH-S288 | CONN EDGECARD EXTEND 86POS 0.156 |

| ACM43DRMD-S288 | CONN EDGECARD EXTEND 86POS 0.156 |

| ACC35DRAN-S734 | CONN EDGECARD 70POS .100 R/A PCB |

相關代理商/技術參數 |

參數描述 |

|---|---|

| A3PE600-PQG896 | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3E Flash Family FPGAs |

| A3PE600-PQG896ES | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3E Flash Family FPGAs |

| A3PE600-PQG896I | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3E Flash Family FPGAs |

| A3PE600-PQG896PP | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3E Flash Family FPGAs |

| A3PE-STARTER-KIT-2 | 功能描述:KIT EVAL FOR A3PE1500 PROASIC3 RoHS:是 類別:編程器,開發系統 >> 通用嵌入式開發板和套件(MCU、DSP、FPGA、CPLD等) 系列:ProASIC3 產品培訓模塊:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色產品:Blackfin? BF50x Series Processors 標準包裝:1 系列:Blackfin® 類型:DSP 適用于相關產品:ADSP-BF548 所含物品:板,軟件,4x4 鍵盤,光學撥輪,QVGA 觸摸屏 LCD 和 40G 硬盤 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相關產品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

發布緊急采購,3分鐘左右您將得到回復。