- 您現在的位置:買賣IC網 > PDF目錄164971 > A3PN125-1VQ100 FPGA, 3072 CLBS, 125000 GATES, PQFP100 PDF資料下載

參數資料

| 型號: | A3PN125-1VQ100 |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| 封裝: | 14 X 14 MM, 1.20 MM HEIGHT, 0.50 MM PITCH, VQFP-100 |

| 文件頁數: | 61/106頁 |

| 文件大小: | 3324K |

| 代理商: | A3PN125-1VQ100 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁當前第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁

ProASIC3 nano DC and Switching Characteristics

2- 44

R e visio n 8

Output Enable Register

Timing Characteristics

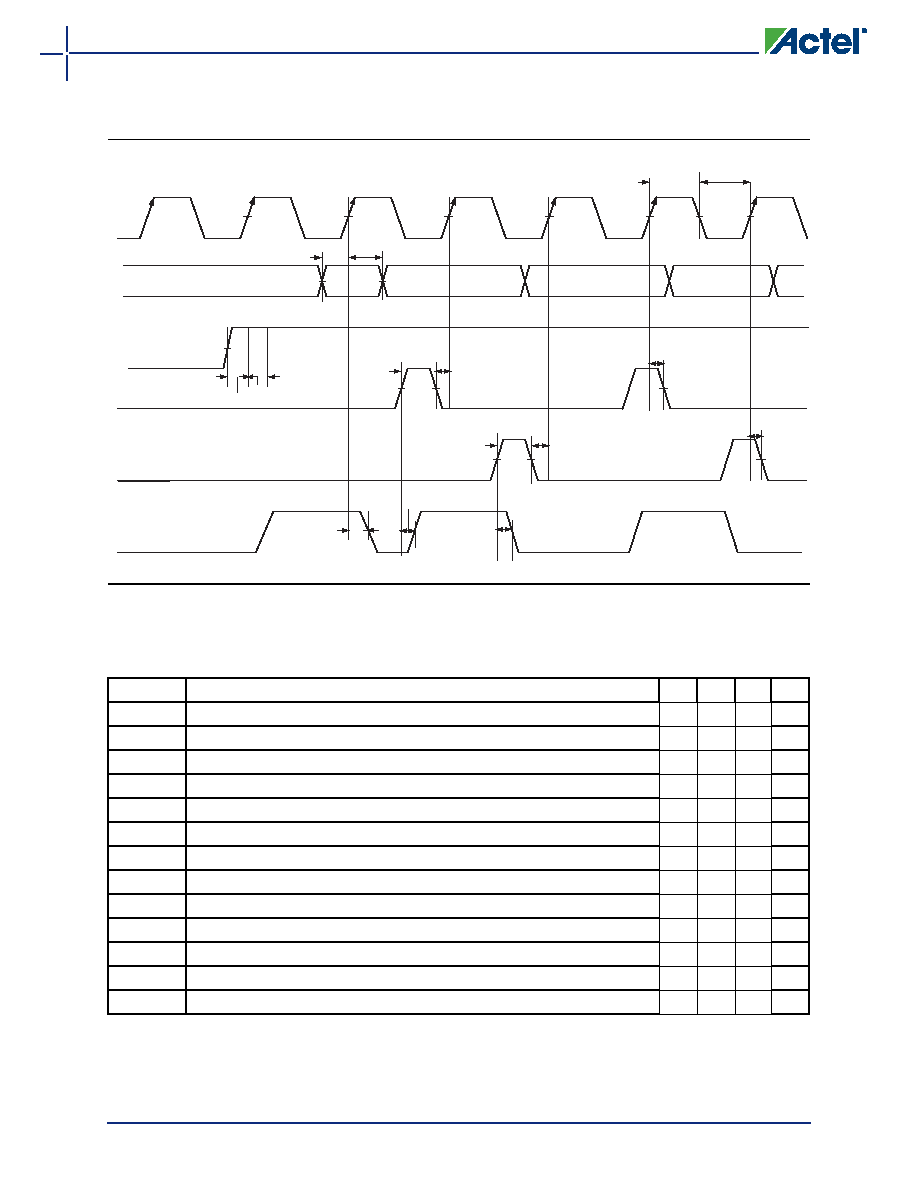

Figure 2-14 Output Enable Register Timing Diagram

50%

Preset

Clear

EOUT

CLK

D_Enable

Enable

tOESUE

50%

tOESUD tOEHD

50%

tOECLKQ

1

0

tOEHE

tOERECPRE

tOEREMPRE

tOERECCLR

tOEREMCLR

tOEWCLR

tOEWPRE

tOEPRE2Q

tOECLR2Q

tOECKMPWH tOECKMPWL

50%

Table 2-60 Output Enable Register Propagation Delays

Commercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

Parameter

Description

–2

–1

Std. Units

tOECLKQ

Clock-to-Q of the Output Enable Register

0.44 0.51 0.59

ns

tOESUD

Data Setup Time for the Output Enable Register

0.31 0.36 0.42

ns

tOEHD

Data Hold Time for the Output Enable Register

0.00 0.00 0.00

ns

tOECLR2Q

Asynchronous Clear-to-Q of the Output Enable Register

0.67 0.76 0.89

ns

tOEPRE2Q

Asynchronous Preset-to-Q of the Output Enable Register

0.67 0.76 0.89

ns

tOEREMCLR Asynchronous Clear Removal Time for the Output Enable Register

0.00 0.00 0.00

ns

tOERECCLR Asynchronous Clear Recovery Time for the Output Enable Register

0.22 0.25 0.30

ns

tOEREMPRE Asynchronous Preset Removal Time for the Output Enable Register

0.00 0.00 0.00

ns

tOERECPRE Asynchronous Preset Recovery Time for the Output Enable Register

0.22 0.25 0.30

ns

tOEWCLR

Asynchronous Clear Minimum Pulse Width for the Output Enable Register

0.22 0.25 0.30

ns

tOEWPRE

Asynchronous Preset Minimum Pulse Width for the Output Enable Register

0.22 0.25 0.30

ns

tOECKMPWH Clock Minimum Pulse Width HIGH for the Output Enable Register

0.36 0.41 0.48

ns

tOECKMPWL Clock Minimum Pulse Width LOW for the Output Enable Register

0.32 0.37 0.43

ns

Note:

For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

相關PDF資料 |

PDF描述 |

|---|---|

| A3PN125-1VQG100I | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-1VQG100 | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-2VQ100I | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-2VQ100 | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-2VQG100I | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| A3PN125-1VQ100I | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:ProASIC3 nano 標準包裝:152 系列:IGLOO PLUS LAB/CLB數:- 邏輯元件/單元數:792 RAM 位總計:- 輸入/輸出數:120 門數:30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應商設備封裝:289-CSP(14x14) |

| A3PN125-1VQG100 | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:ProASIC3 nano 標準包裝:152 系列:IGLOO PLUS LAB/CLB數:- 邏輯元件/單元數:792 RAM 位總計:- 輸入/輸出數:120 門數:30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應商設備封裝:289-CSP(14x14) |

| A3PN125-1VQG100I | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:ProASIC3 nano 標準包裝:152 系列:IGLOO PLUS LAB/CLB數:- 邏輯元件/單元數:792 RAM 位總計:- 輸入/輸出數:120 門數:30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應商設備封裝:289-CSP(14x14) |

| A3PN125-2VQ100 | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:ProASIC3 nano 標準包裝:152 系列:IGLOO PLUS LAB/CLB數:- 邏輯元件/單元數:792 RAM 位總計:- 輸入/輸出數:120 門數:30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應商設備封裝:289-CSP(14x14) |

| A3PN125-2VQ100I | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:ProASIC3 nano 標準包裝:152 系列:IGLOO PLUS LAB/CLB數:- 邏輯元件/單元數:792 RAM 位總計:- 輸入/輸出數:120 門數:30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應商設備封裝:289-CSP(14x14) |

發布緊急采購,3分鐘左右您將得到回復。