- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4528 > A3PN125-2VQ100I (Microsemi SoC)IC FPGA NANO 125K GATES 100-VQFP PDF資料下載

參數(shù)資料

| 型號(hào): | A3PN125-2VQ100I |

| 廠商: | Microsemi SoC |

| 文件頁數(shù): | 1/114頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA NANO 125K GATES 100-VQFP |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | ProASIC3 nano |

| RAM 位總計(jì): | 36864 |

| 輸入/輸出數(shù): | 71 |

| 門數(shù): | 125000 |

| 電源電壓: | 1.425 V ~ 1.575 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 100-TQFP |

| 供應(yīng)商設(shè)備封裝: | 100-VQFP(14x14) |

當(dāng)前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁

January 2013

I

2013 Microsemi Corporation

ProASIC3 nano Flash FPGAs

Features and Benefits

Wide Range of Features

10 k to 250 k System Gates

Up to 36 kbits of True Dual-Port SRAM

Up to 71 User I/Os

Reprogrammable Flash Technology

130-nm, 7-Layer Metal (6 Copper), Flash-Based CMOS

Process

Instant On Level 0 Support

Single-Chip Solution

Retains Programmed Design when Powered Off

High Performance

350 MHz System Performance

In-System Programming (ISP) and Security

ISP Using On-Chip 128-Bit Advanced Encryption Standard

(AES) Decryption via JTAG (IEEE 1532–compliant)

FlashLock Designed to Secure FPGA Contents

Low Power

Low Power ProASIC3 nano Products

1.5 V Core Voltage for Low Power

Support for 1.5 V-Only Systems

Low-Impedance Flash Switches

High-Performance Routing Hierarchy

Segmented, Hierarchical Routing and Clock Structure

Advanced I/Os

1.5 V, 1.8 V, 2.5 V, and 3.3 V Mixed-Voltage Operation

Bank-Selectable I/O Voltages—up to 4 Banks per Chip

Single-Ended

I/O

Standards:

LVTTL,

LVCMOS

3.3 V /

2.5 V / 1.8 V / 1.5 V

Wide Range Power Supply Voltage Support per JESD8-B,

Allowing I/Os to Operate from 2.7 V to 3.6 V

I/O Registers on Input, Output, and Enable Paths

Selectable Schmitt Trigger Inputs

Hot-Swappable and Cold-Sparing I/Os

Weak Pull-Up/-Down

IEEE 1149.1 (JTAG) Boundary Scan Test

Pin-Compatible Packages across the ProASIC3 Family

Clock Conditioning Circuit (CCC) and PLL

Up to Six CCC Blocks, One with an Integrated PLL

Configurable Phase Shift, Multiply/Divide, Delay

Capabilities and External Feedback

Wide Input Frequency Range (1.5 MHz to 350 MHz)

Embedded Memory

1 kbit of FlashROM User Nonvolatile Memory

SRAMs and FIFOs with Variable-Aspect-Ratio 4,608-Bit RAM

True Dual-Port SRAM (except ×18 organization)

Enhanced Commercial Temperature Range

–20°C to +70°C

A3PN030 and smaller devices do not support this feature.

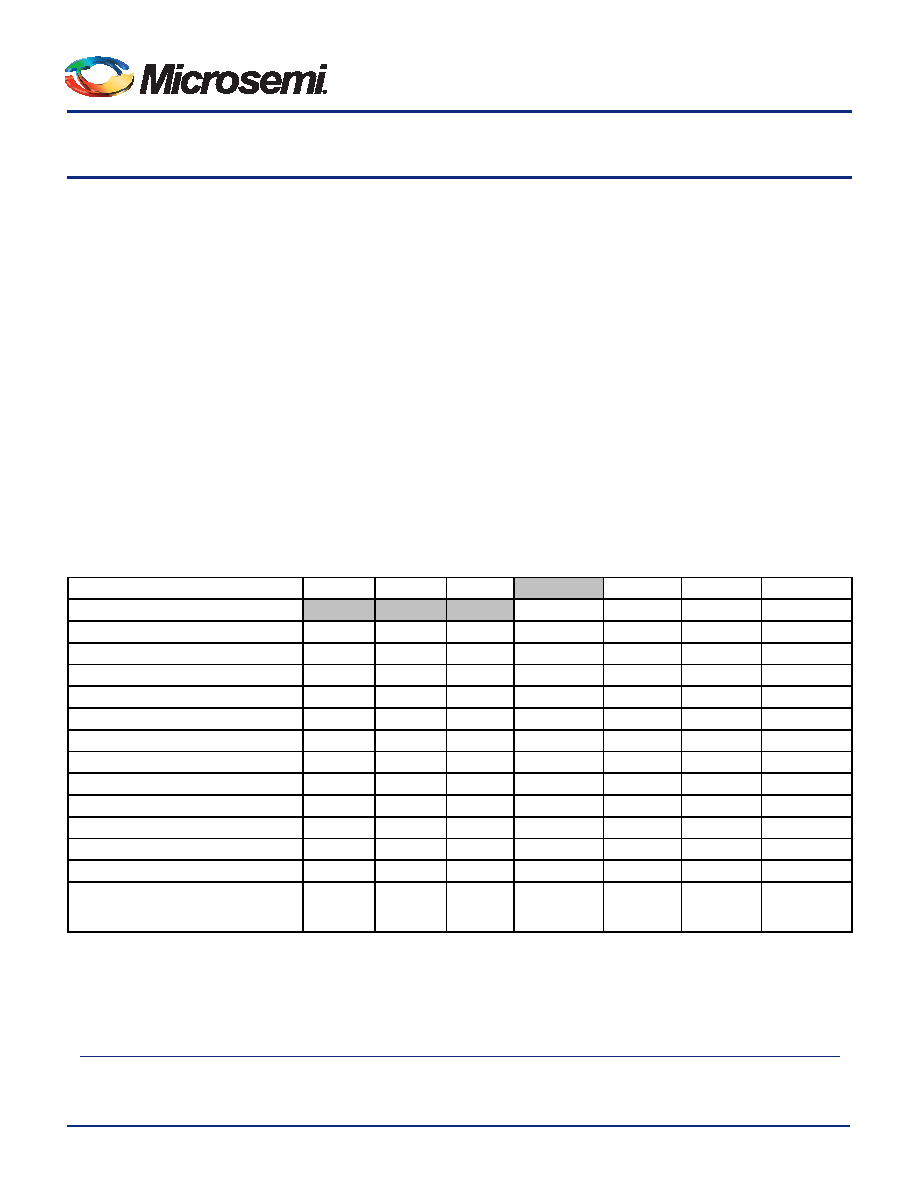

Table 1 ProASIC3 nano Devices

ProASIC3 nano Devices

A3PN010 A3PN0151 A3PN020

A3PN060

A3PN125

A3PN250

ProASIC3 nano-Z Devices1

A3PN030Z1,2 A3PN060Z1 A3PN125Z1

A3N250Z1

System Gates

10,000

15,000

20,000

30,000

60,000

125,000

250,000

Typical Equivalent Macrocells

86

128

172

256

512

1,024

2,048

VersaTiles (D-flip-flops)

260

384

520

768

1,536

3,072

6,144

RAM Kbits (1,024 bits)2

–

18

36

4,608-Bit Blocks2

––

–

4

8

FlashROM Kbits

1

Secure (AES) ISP2

––

–

Yes

Integrated PLL in CCCs2

––

–

1

VersaNet Globals

4

6

18

I/O Banks

2

3

2

4

Maximum User I/Os (packaged device)

34

49

77

71

68

Maximum User I/Os (Known Good Die)

34

–

52

83

71

68

Package Pins

QFN

VQFP

QN48

QN68

QN48, QN68

VQ100

Notes:

1. Not recommended for new designs.

2. A3PN030Z and smaller devices do not support this feature.

3. For higher densities and support of additional features, refer to the ProASIC3 and ProASIC3E datasheets.

Revision 11

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M1A3P250-2VQ100 | IC FPGA 1KB FLASH 250K 100-VQFP |

| A3P250-2VQG100 | IC FPGA 1KB FLASH 250K 100-VQFP |

| A3PN125-2VQG100I | IC FPGA NANO 125K GATES 100-VQFP |

| BR24T128FVJ-WE2 | IC EEPROM I2C 128K 400KHZ 8TSSOP |

| AGLN060V2-ZVQG100I | IC FPGA NANO 1KB 60K 100VQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A3PN125-2VQG100 | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ProASIC3 nano 標(biāo)準(zhǔn)包裝:152 系列:IGLOO PLUS LAB/CLB數(shù):- 邏輯元件/單元數(shù):792 RAM 位總計(jì):- 輸入/輸出數(shù):120 門數(shù):30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應(yīng)商設(shè)備封裝:289-CSP(14x14) |

| A3PN125-2VQG100I | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ProASIC3 nano 標(biāo)準(zhǔn)包裝:152 系列:IGLOO PLUS LAB/CLB數(shù):- 邏輯元件/單元數(shù):792 RAM 位總計(jì):- 輸入/輸出數(shù):120 門數(shù):30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應(yīng)商設(shè)備封裝:289-CSP(14x14) |

| A3PN125-DIELOT | 制造商:Microsemi Corporation 功能描述:A3PN125-DIELOT - Gel-pak, waffle pack, wafer, diced wafer on film |

| A3PN125-VQ100 | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ProASIC3 nano 標(biāo)準(zhǔn)包裝:152 系列:IGLOO PLUS LAB/CLB數(shù):- 邏輯元件/單元數(shù):792 RAM 位總計(jì):- 輸入/輸出數(shù):120 門數(shù):30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應(yīng)商設(shè)備封裝:289-CSP(14x14) |

| A3PN125-VQ100I | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ProASIC3 nano 標(biāo)準(zhǔn)包裝:152 系列:IGLOO PLUS LAB/CLB數(shù):- 邏輯元件/單元數(shù):792 RAM 位總計(jì):- 輸入/輸出數(shù):120 門數(shù):30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應(yīng)商設(shè)備封裝:289-CSP(14x14) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。