- 您現在的位置:買賣IC網 > PDF目錄366309 > A8255 (Altera Corporation) PROGRAMMABLE PERIPHERAL INTERFACE ADAPTER PDF資料下載

參數資料

| 型號: | A8255 |

| 廠商: | Altera Corporation |

| 英文描述: | PROGRAMMABLE PERIPHERAL INTERFACE ADAPTER |

| 中文描述: | 可編程外圍接口適配器 |

| 文件頁數: | 1/13頁 |

| 文件大小: | 250K |

| 代理商: | A8255 |

Altera Corporation

45

a8255

Programmable Peripheral

Interface Adapter

September 1996, ver. 1

A-DS-A8255-01

Features

I

a8255

peripheral interface adapter

Optimized for FLEX

24 programmable inputs/outputs

Static read/write or handshaking modes

Direct bit set/reset capability

Synchronous design

Uses approximately 194 FLEX logic elements (LEs)

Functionally based on the Intel 8255A and Harris 82C55A devices,

except as noted in the

“Variations & Clarifications” section on

page 56

MegaCore function implementing a programmable

I

I

I

I

I

I

I

and MAX

architectures

General

Description

The

interface adapter (see

Figure 1

). The

programmed in two groups of 12. This MegaCore function operates in the

following three modes:

a8255

MegaCore function implements a programmable peripheral

a8255

has 24 I/O signals that can be

I

Mode 0: Basic Input/Output

lower) can be independently configured as inputs or outputs to read

or hold static data. Outputs are registered; inputs are not registered.

Mode 1: Strobed Input/Output

—Port A and port B can be

independently configured as strobed input or output buses. Signals

from port C are dedicated as control signals for data handshaking.

Mode 2: Bidirectional Bus

—Port A can be configured as a bidirectional

bus with the majority of port C providing the control signals. In this

configuration, port B can still implement mode 0 or mode 1.

—Port A, port B, and port C (upper and

I

I

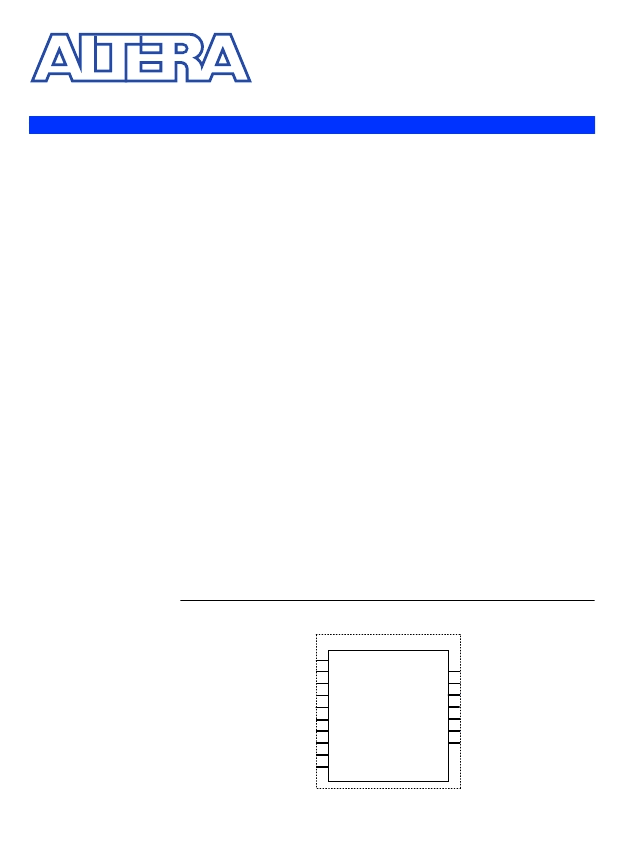

Figure 1. a8255 Symbol

PAEN

PBEN

DOUT[7..0]

PAOUT[7..0]

PBOUT[7..0]

PCEN[7..0]

PCOUT[7..0]

A8255

CLK

nCS

nRD

nWR

RESET

A[1..0]

DIN[7..0]

PAin[7..0]

PBin[7..0]

PCin[7..0]

相關PDF資料 |

PDF描述 |

|---|---|

| a8259 | Programmable Interrupt Controller(可編程中斷控制器) |

| A8406-53 | Various types of cables for frame grabber |

| A8406-54 | Various types of cables for frame grabber |

| A8406-55 | Various types of cables for frame grabber |

| A8406-56 | Various types of cables for frame grabber |

相關代理商/技術參數 |

參數描述 |

|---|---|

| A82564000AP | 制造商:Panasonic Industrial Company 功能描述:LEVER |

| A82564210AP | 制造商:Panasonic Industrial Company 功能描述:LEVER |

| A82565540AP | 制造商:Panasonic Industrial Company 功能描述:LEVER |

| A8259 | 制造商:ALTERA 制造商全稱:Altera Corporation 功能描述:PROGRAMMABLE INTERRUPT CONTROLLER |

| A82596CA-16 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

發布緊急采購,3分鐘左右您將得到回復。