- 您現在的位置:買賣IC網 > PDF目錄373911 > AD7641BSTZ (ANALOG DEVICES INC) 18-Bit 250/670 kSPS PulSAR Bipolar Programmable Inputs ADC PDF資料下載

參數資料

| 型號: | AD7641BSTZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 18-Bit 250/670 kSPS PulSAR Bipolar Programmable Inputs ADC |

| 中文描述: | 1-CH 18-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, PQFP48 |

| 封裝: | LEAD FREE, MS-026BBC, LQFP-48 |

| 文件頁數: | 10/14頁 |

| 文件大小: | 192K |

| 代理商: | AD7641BSTZ |

AD7631/AD7634

Preliminary Technical Data

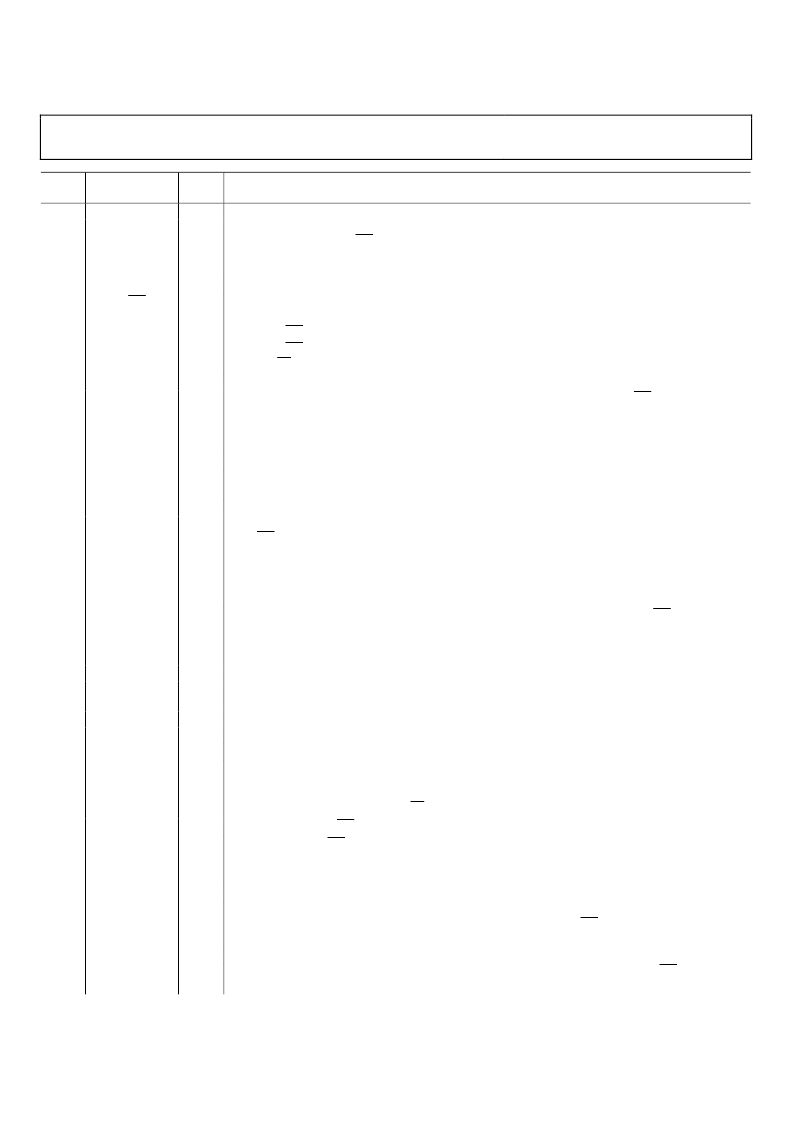

Pin

No.

11, 12

Rev. PrC | Page 10 of 14

Mnemonic

D[4:5]

or DIVSCLK[0:1]

Type

1

DI/O

Description

When MODE[1:0] = 0, 1, or 2, these pins are Bit 4 and Bit 5 of the parallel port data output bus.

When MODE[1:0] = 3 (serial mode), serial clock division selection. When using serial master read

after convert mode (EXT/INT = low, RDC/SDIN = low), these inputs can be used to slow down the

internally generated serial clock that clocks the data output. In other serial modes, these pins are

high impedance outputs.

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 6 of the parallel port data output bus.

When MODE[1:0] = 3 (serial mode), serial clock source select. This input is used to select the

internally generated (master) or external (slave) serial data clock.

When EXT/INT = low, master mode. The internal serial clock is selected on SCLK output.

When EXT/INT = high, slave mode. The output data is synchronized to an external clock signal,

gated by CS, connected to the SCLK input.

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 7 of the parallel port data output bus.

When MODE[1:0] = 3 (serial mode), invert sync select. In serial master mode (EXT/INT = low), this

input is used to select the active state of the SYNC signal.

When INVSYNC = low, SYNC is active high.

When INVSYNC = high, SYNC is active low.

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 8 of the parallel port data output bus.

When MODE[1:0] = 3, invert SCLK select. In all serial modes, this input is used to

invert the SCLK signal.

When MODE[1:0] = 0, 1, or 2, this output is used as bit 9 of the parallel port data output bus.

When MODE[1:0] = 3 (serial mode), read during convert. When using serial master mode

(EXT/INT = low), RDC is used to select the read mode.

When RDC = high, the previous conversion result is output on SDOUT during conversion and

the period of SCLK changes.

When RDC = low (read after convert), the current result can be output on SDOUT only when

the conversion is complete.

When MODE[1:0] = 3 (serial mode), serial data in. When using serial slave mode, (EXT/INT = high),

SDIN could be used as a data input to daisy-chain the conversion results from two or more ADCs

onto a single SDOUT line. The digital data level on SDIN is output on SDOUT with a delay of 18 SCLK

periods after the initiation of the read sequence.

Input/Output Interface Digital Power Ground.

Input/Output Interface Digital Power. Nominally at the same supply as the supply of the

host interface (2.7 V to 5V).

Digital Power. Nominally at 5 V.

Digital Power Ground.

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 10 of the parallel port data output bus.

When MODE[1:0] = 3 (serial mode), serial data output. In serial mode, this pin is used as the serial

data output synchronized to SCLK. Conversion results are stored in an on-chip register. The ADC

provides the conversion result, MSB first, from its internal shift register. The data format is

determined by the logic level of OB/2C.

In master mode, EXT/INT = low. SDOUT is valid on both edges of SCLK.

In slave mode, EXT/INT = high:

When INVSCLK = low, SDOUT is updated on SCLK rising edge and valid on the next falling edge.

When INVSCLK = high, SDOUT is updated on SCLK falling edge and valid on the next rising edge.

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 11 of the parallel port data output bus.

When MODE[1:0] = 3 (serial mode), serial clock. In all serial modes, this pin is used as the serial

data clock input or output, depending upon the logic state of the EXT/INT pin. The active edge

where the data SDOUT is updated depends on the logic state of the INVSCLK pin.

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 12 of the parallel port data output bus.

When MODE[1:0] = 3 (serial mode), frame synchronization. In serial master mode (EXT/INT= low),

this output is used as a digital output frame synchronization for use with the internal data clock.

13

D6

or EXT/INT

DI/O

14

D7

or INVSYNC

DI/O

15

D8

or INVSCLK

DI/O

16

D9

or RDC

DI/O

or SDIN

17

18

OGND

OVDD

P

P

19

20

21

DVDD

DGND

D10

or SDOUT

P

P

DO

22

D11

or SCLK

DI/O

23

D12

or SYNC

DO

相關PDF資料 |

PDF描述 |

|---|---|

| AD7641BSTZRL | 18-Bit 250/670 kSPS PulSAR Bipolar Programmable Inputs ADC |

| AD7641 | 18-Bit, 2 MSPS SAR ADC |

| AD7641ACP | 18-Bit, 2 MSPS SAR ADC |

| AD7641ACPRL | ECONOLINE: REC2.2-S_DRW(Z)/H* - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- 4.5-9V, 9-18V, 18-36V, 36-72V Wide Input Range 2 : 1- UL94V-0 Package Material- Continuous Short Circiut Protection- Cost Effective- 100% Burned In- Efficiency to 84% |

| AD7641AST | 18-Bit, 2 MSPS SAR ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7641BSTZRL | 功能描述:IC ADC 18BIT 2MSPS SAR 48-LQFP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7641XST | 制造商:Analog Devices 功能描述: |

| AD7641XST-U3 | 制造商:Analog Devices 功能描述: |

| AD7643 | 制造商:AD 制造商全稱:Analog Devices 功能描述:14-Bit, 1 MSPS, Differential, Programmable Input PulSAR ADC |

| AD7643BCPZ | 功能描述:IC ADC 18BIT DIFF W/REF 48LFCSP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:PulSAR® 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

發布緊急采購,3分鐘左右您將得到回復。