- 您現在的位置:買賣IC網 > PDF目錄373914 > AD7712 (Analog Devices, Inc.) Signal Conditioning ADC(LC2MOS信號調節A/D轉換器) PDF資料下載

參數資料

| 型號: | AD7712 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Signal Conditioning ADC(LC2MOS信號調節A/D轉換器) |

| 中文描述: | 信號調理模數轉換器(LC2MOS信號調節的A / D轉換器) |

| 文件頁數: | 3/28頁 |

| 文件大小: | 242K |

| 代理商: | AD7712 |

第1頁第2頁當前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

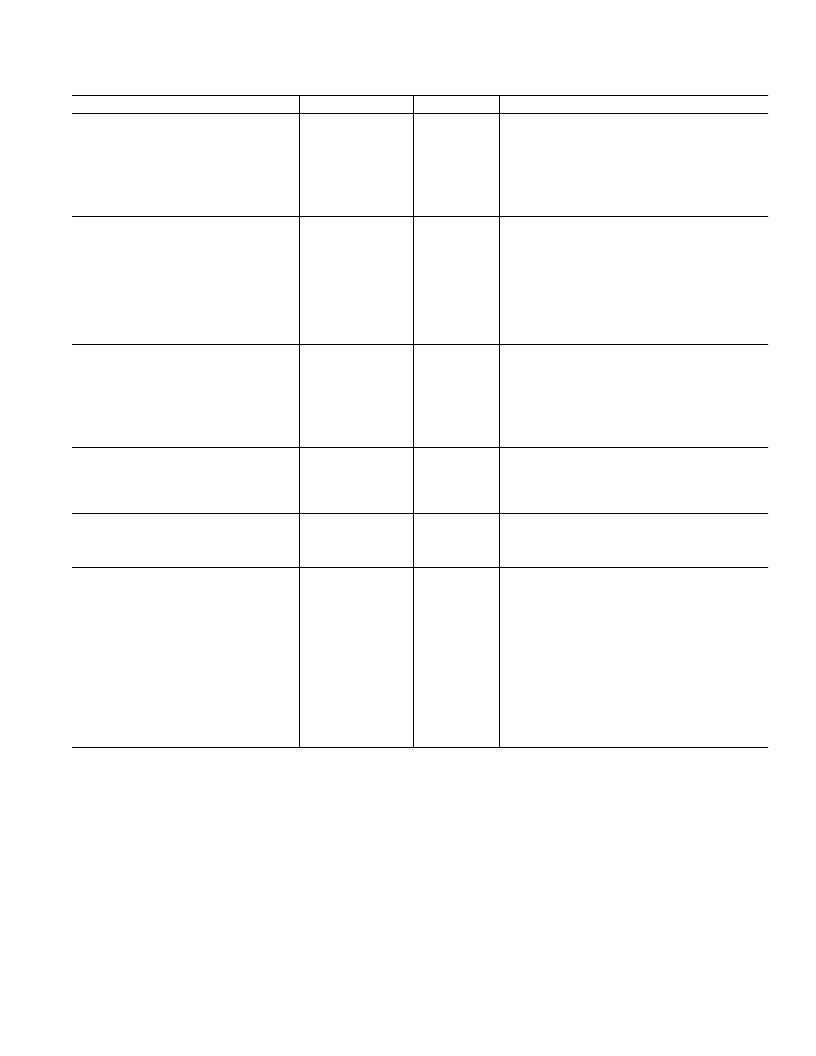

Parameter

REFERENCE OUTPUT

Output Voltage

Initial Tolerance

Drift

Output Noise

Line Regulation (AV

DD

)

Load Regulation

External Current

V

BIAS

INPUT

13

A, S Versions

1

Units

Conditions/Comments

2.5

±

1

20

30

1

1.5

1

V nom

% max

ppm/

°

C typ

μ

V typ

mV/V max

mV/mA max

mA max

pk-pk Noise; 0.1 Hz to 10 Hz Bandwidth

Maximum Load Current 1 mA

AV

– 0.85

×

V

REF

or AV

DD

– 3.5

See V

Input Section

Whichever Is Smaller; +5 V/–5 V or +10 V/0 V

Nominal AV

/V

Whichever Is Smaller; +5 V/0 V Nominal AV

DD

/V

SS

See V

Input Section

Whichever Is Greater; +5 V/–5 V or +10 V/0 V

Nominal AV

DD

/V

SS

Whichever Is Greater; +5 V/0 V Nominal AV

DD

/V

SS

Increasing with Gain

V max

or AV

– 2.1

V

+ 0.85

×

V

REF

or V

SS

+ 3

V max

V min

or V

SS

+ 2.1

65 to 85

V min

dB typ

V

BIAS

Rejection

LOGIC INPUTS

Input Current

All Inputs except MCLK IN

V

INL

, Input Low Voltage

V

, Input High Voltage

MCLK IN Only

V

INL

, Input Low Voltage

V

INH

, Input High Voltage

LOGIC OUTPUTS

V

OL

, Output Low Voltage

V

, Output High Voltage

Floating State Leakage Current

Floating State Output Capacitance

14

TRANSDUCER BURNOUT

Current

Initial Tolerance

Drift

SYSTEM CALIBRATION

AIN1

Positive Full-Scale Calibration Limit

15

Negative Full-Scale Calibration Limit

15

Offset Calibration Limit

16, 17

Input Span

15

±

10

μ

A max

0.8

2.0

V max

V min

0.8

3.5

V max

V min

0.4

4.0

±

10

9

V max

V min

μ

A max

pF typ

I

SINK

= 1.6 mA

I

SOURCE

= 100

μ

A

4.5

±

10

0.1

μ

A nom

% typ

%/

°

C typ

(1.05

×

V

REF

)/GAIN

–(1.05

×

V

REF

)/GAIN

–(1.05

×

V

REF

)/GAIN

0.8

×

V

REF

/GAIN

(2.1

×

V

REF

)/GAIN

V max

V max

V max

V min

V max

GAIN Is the Selected PGA Gain (Between 1 and 128)

GAIN Is the Selected PGA Gain (Between 1 and 128)

GAIN Is the Selected PGA Gain (Between 1 and 128)

GAIN Is the Selected PGA Gain (Between 1 and 128)

GAIN Is the Selected PGA Gain (Between 1 and 128)

AIN2

Positive Full-Scale Calibration Limit

15

Negative Full-Scale Calibration Limit

15

Offset Calibration Limit

17

Input Span

15

(4.2

×

V

REF

)/GAIN

–(4.2

×

V

REF

)/GAIN

–(4.2

×

V

REF

)/GAIN

3.2

×

V

REF

/GAIN

(8.4

×

V

REF

)/GAIN

V max

V max

V max

V min

V max

GAIN Is the Selected PGA Gain (Between 1 and 128)

GAIN Is the Selected PGA Gain (Between 1 and 128)

GAIN Is the Selected PGA Gain (Between 1 and 128)

GAIN Is the Selected PGA Gain (Between 1 and 128)

GAIN Is the Selected PGA Gain (Between 1 and 128)

NOTES

13

The AD7712 is tested with the following V

voltages. With AV

DD

= +5 V and V

SS

= 0 V, V

BIAS

= +2.5 V; with AV

DD

= +10 V and V

SS

= 0 V, V

BIAS

= +5 V and

with AV

= +5 V and V

= –5 V, V

= 0 V.

14

Guaranteed by design, not production tested.

15

After calibration, if the analog input exceeds positive full scale, the converter will output all 1s. If the analog input is less than negative full scale, then the device will

output all 0s.

16

These calibration and span limits apply provided the absolute voltage on the AIN1 analog inputs does not exceed AV

DD

+ 30 mV or does not go more negative

than V

– 30 mV.

17

The offset calibration limit applies to both the unipolar zero point and the bipolar zero point.

AD7712

–3–

REV. E

相關PDF資料 |

PDF描述 |

|---|---|

| AD7713* | LC2MOS Loop-Powered Signal Conditioning ADC |

| AD7713AN | LC2MOS Loop-Powered Signal Conditioning ADC |

| AD7713AQ | LC2MOS Loop-Powered Signal Conditioning ADC |

| AD7713AR | LC2MOS Loop-Powered Signal Conditioning ADC |

| AD7713SQ | LC2MOS Loop-Powered Signal Conditioning ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7712_04 | 制造商:AD 制造商全稱:Analog Devices 功能描述:LC2MOS Signal Conditioning ADC |

| AD7712AN | 功能描述:IC ADC SIGNAL COND LC2MOS 24-DIP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7712ANZ | 功能描述:IC ADC SIGNAL COND LC2MOS 24-DIP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 其它有關文件:TSA1204 View All Specifications 標準包裝:1 系列:- 位數:12 采樣率(每秒):20M 數據接口:并聯 轉換器數目:2 功率耗散(最大):155mW 電壓電源:模擬和數字 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-TQFP 供應商設備封裝:48-TQFP(7x7) 包裝:Digi-Reel® 輸入數目和類型:4 個單端,單極;2 個差分,單極 產品目錄頁面:1156 (CN2011-ZH PDF) 其它名稱:497-5435-6 |

| AD7712ANZ | 制造商:Analog Devices 功能描述:IC ADC 24-BIT SIGMA DELTA |

發布緊急采購,3分鐘左右您將得到回復。