- 您現在的位置:買賣IC網 > PDF目錄373916 > AD7787 (Analog Devices, Inc.) Low Power, 2-Channel 24-Bit Sigma-Delta ADC PDF資料下載

參數資料

| 型號: | AD7787 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Low Power, 2-Channel 24-Bit Sigma-Delta ADC |

| 中文描述: | 低功耗,雙通道24位Σ-Δ模數轉換器 |

| 文件頁數: | 13/20頁 |

| 文件大小: | 326K |

| 代理商: | AD7787 |

AD7787

Rev. 0 | Page 13 of 20

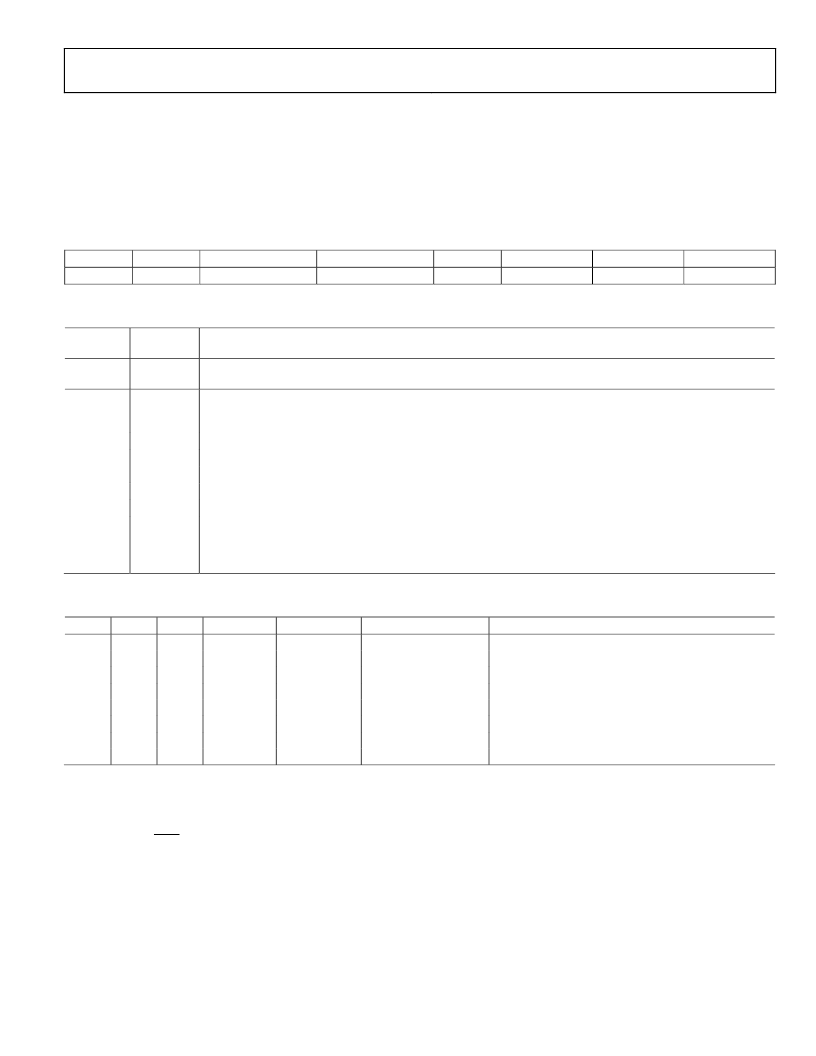

FILTER REGISTER (RS1, RS0 = 1, 0; POWER-ON/RESET = 0×04)

The filter register is an 8-bit register from which data can be read or to which data can be written. This register is used to set the output

word rate. Table 11 outlines the bit designations for the filter register. FR0 through FR7 indicate the bit locations, FR denoting the bits are

in the filter register. FR7 denotes the first bit of the data stream. The number in the parenthesis indicates the power-on/reset default status

of that bit.

FR7

0 (0)

FR6

0 (0)

FR5

CDIV1 (0)

FR4

CDIV0 (0)

FR3

0 (0)

FR2

FS2 (1)

FR1

FS1 (0)

FR0

FS0 (0)

Table 11. Filter Register Bit Designations

Bit

Location

Bit Name

FR7 to

FR6

FR5 to

FR4

to CDIV0

Description

These bits must be programmed with a Logic 0 for correct operation.

0

CLKDIV1

These bits are used to operate the AD7787 in the lower power modes. The clock is internally divided and the

power is reduced. In the low power modes, the update rates will scale with the clock frequency so that dividing

the clock by 2 causes the update rate to be reduced by a factor of 2 also.

00

Normal Mode

01

Clock Divided by 2

10

Clock Divided by 4

11

Clock Divided by 8

This bit must be programmed with a Logic 0 for correct operation.

These bits set the output word rate of the ADC. The update rate influences the 50 Hz/60 Hz rejection and the

noise. Table 12 shows the allowable update rates when normal power mode is used. In the low power modes,

the update rate is scaled with the clock frequency. For example, if the internal clock is divided by a factor of 2,

the corresponding update rates are divided by 2 also.

FR3

FR2 to

FR0

0

FS2 to FS0

Table 12. Update Rates

FS2

FS1

0

0

0

0

0

1

0

1

1

0

1

0

1

1

1

1

FS0

0

1

0

1

0

1

0

1

f

ADC

(Hz)

120

100

33.3

20

16.6

16.7

13.3

9.5

f3dB (Hz)

28

24

8

4.7

4

4

3.2

2.3

RMS Noise (μV)

40

25

3.36

1.6

1.5

1.5

1.2

1.1

Rejection

25 dB @ 60 Hz

25 dB @ 50 Hz

80 dB @ 60 Hz

65 dB @ 50 Hz/60 Hz (Default Setting)

80 dB @ 50 Hz

67 dB @ 50 Hz/60 Hz

DATA REGISTER (RS1, RS0 = 1, 1; POWER-ON/RESET = 0×000000)

The conversion result from the ADC is stored in this data register. This is a read-only register. On completion of a read operation from

this register, the RDY bit/pin is set.

相關PDF資料 |

PDF描述 |

|---|---|

| AD7789 | Low Power, 16-/24-Bit Sigma-Delta ADC |

| AD7788 | Low Power, 16-/24-Bit Sigma-Delta ADC |

| AD7788ARM | Low Power, 16-/24-Bit Sigma-Delta ADC |

| AD7788ARM-REEL | Low Power, 16-/24-Bit Sigma-Delta ADC |

| AD7789BRM | Low Power, 16-/24-Bit Sigma-Delta ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7787_13 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Low Power, 2-Channel 24-Bit Sigma-Delta ADC |

| AD7787BRM | 功能描述:IC ADC 24BIT LP 2CH SIG 10-MSOP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:16 采樣率(每秒):45k 數據接口:串行 轉換器數目:2 功率耗散(最大):315mW 電壓電源:模擬和數字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應商設備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數目和類型:2 個單端,單極 |

| AD7787BRM-REEL | 功能描述:IC ADC 24BIT LP 2CH SIG 10-MSOP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:16 采樣率(每秒):45k 數據接口:串行 轉換器數目:2 功率耗散(最大):315mW 電壓電源:模擬和數字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應商設備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數目和類型:2 個單端,單極 |

| AD7787BRMZ | 功能描述:IC ADC 24BIT 2CH LP SIG 10MSOP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:16 采樣率(每秒):45k 數據接口:串行 轉換器數目:2 功率耗散(最大):315mW 電壓電源:模擬和數字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應商設備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數目和類型:2 個單端,單極 |

| AD7787BRMZ | 制造商:Analog Devices 功能描述:IC 24BIT ADC SMD 7787 MSOP10 |

發布緊急采購,3分鐘左右您將得到回復。