- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373918 > AD7824UQ (ANALOG DEVICES INC) LC2MOS High Speed 4- & 8-Channel 8-Bit ADCs PDF資料下載

參數(shù)資料

| 型號: | AD7824UQ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | LC2MOS High Speed 4- & 8-Channel 8-Bit ADCs |

| 中文描述: | 4-CH 8-BIT FLASH METHOD ADC, PARALLEL ACCESS, CDIP24 |

| 封裝: | 0.300 INCH, SKINNY, CERDIP-24 |

| 文件頁數(shù): | 9/16頁 |

| 文件大小: | 270K |

| 代理商: | AD7824UQ |

AD7824/AD7828

REV. F

–9–

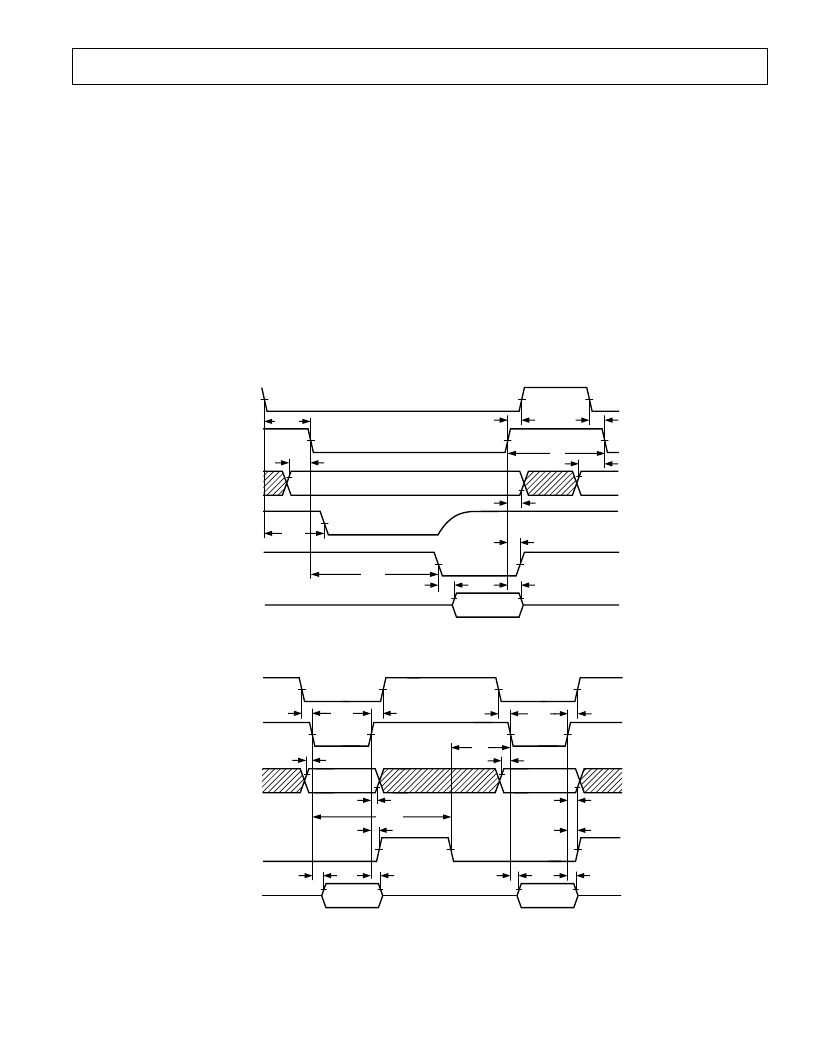

MODE 0

Figure 14 shows the timing diagram for Mode 0 operation. This

mode can only be used for microprocessors that have a WAIT

state facility, whereby a READ instruction cycle can be extended

to accommodate slow memory devices. A READ operation brings

CS

and

RD

low, which starts a conversion. The analog multiplexer

address inputs must remain valid while

CS

and

RD

are low. The

data bus (DB7–DB0) remains in the three-state condition until

conversion is complete. There are two converter status outputs on

the AD7824/AD7828, interrupt (

INT

) and ready (RDY), which

can be used to drive the microprocessor READY/WAIT input.

The RDY is an open-drain output (no internal pull-up device) that

goes low on the falling edge of

CS

and goes high impedance at the

end of conversion when the 8-bit conversion result appears on the

data outputs. If the RDY status is not required, the external

pull-up resistor can be omitted and the RDY output tied to GND.

The

INT

goes low when conversion is complete and returns high

on the rising edge of

CS

or

RD

.

MODE 1

Mode 1 operation is designed for applications where the micropro-

cessor is not forced into a WAIT state. A READ operation takes

CS

and

RD

low, which triggers a conversion (see Figure 15). The

multiplexer address inputs are latched on the rising edge of

RD

.

Data from the previous conversion is read from the three-state

data outputs (DB7–DB0). This data may be disregarded if not

required. Note that the RDY output (open drain output) does

not provide any status information in this mode and must be

connected to GND. At the end of conversion,

INT

goes low. A

second READ operation is required to access the new conversion

result. This READ operation latches a new address into the multi-

plexer inputs and starts another conversion.

INT

returns high at the

end of the second READ operation, when

CS

or

RD

returns high.

A delay of 2.5

μ

s must be allowed between READ operations.

CS

RD

ANALOG

CHANNEL

ADDRESS

RDY

INT

DATA

t

CSS

t

AS

t

RDY

t

CRD

t

ACC2

t

DH

t

INTH

t

AH

t

AS

t

P

t

CSS

t

CSH

ADDRESS

VALID

ADDRESS

VALID

DATA

VALID

HIGH IMPEDANCE

Figure 14. Mode 0 Timing Diagram

CS

RD

ANALOG

CHANNEL

ADDRESS

INT

DATA

t

CSS

t

AS

ADDRESS

VALID

OLD

VALID

ADDRESS

VALID

NEW

VALID

t

CSH

t

AH

t

RD

t

CRD

t

INTH

t

ACC1

t

DH

t

ACC1

t

DH

t

INTH

t

AH

t

AS

t

P

t

CSS

t

RD

t

CSH

Figure 15. Mode 1 Timing Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7828KN | LC2MOS High Speed 4- & 8-Channel 8-Bit ADCs |

| AD7828TE | LC2MOS High Speed 4- & 8-Channel 8-Bit ADCs |

| AD7828TQ | LC2MOS High Speed 4- & 8-Channel 8-Bit ADCs |

| AD7824LN | LC2MOS High Speed 4- & 8-Channel 8-Bit ADCs |

| AD7828 | 2.7V-5.25V Digital, 5V Analog, 12 Bit, 4MSPS, Parallel ADC with Ref 48-TQFP -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7824UQ/883 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single-Ended Data Acquisition System |

| AD7824UQ/883B | 制造商:AD 制造商全稱:Analog Devices 功能描述:LC2MOS High Speed 4- & 8-Channel 8-Bit ADCs |

| AD7825 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, 2 MSPS, 8-Bit, 1-, 4-, 8-Channel Sampling ADCs |

| AD7825BN | 制造商:Analog Devices 功能描述:ADC Single Semiflash 2Msps 8-bit Parallel 24-Pin PDIP 制造商:Rochester Electronics LLC 功能描述:4 CHNL PARALLEL 2 MSPS 8-BIT ADC. I.C. - Bulk 制造商:Analog Devices 功能描述:IC 8BIT ADC 7825 DIP24 |

| AD7825BNZ | 制造商:Analog Devices 功能描述:ADC Single Semiflash 2Msps 8-bit Parallel 24-Pin PDIP 制造商:Analog Devices 功能描述:IC 8BIT ADC 7825 DIP24 |

發(fā)布緊急采購,3分鐘左右您將得到回復。