- 您現在的位置:買賣IC網 > PDF目錄373919 > AD7841 (Analog Devices, Inc.) Octal 14-Bit, Parallel Input, Voltage-Output DAC PDF資料下載

參數資料

| 型號: | AD7841 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Octal 14-Bit, Parallel Input, Voltage-Output DAC |

| 中文描述: | 八路14位,并行輸入,電壓輸出DAC |

| 文件頁數: | 3/12頁 |

| 文件大小: | 151K |

| 代理商: | AD7841 |

–3–

REV. 0

AD7841

(These characteristics are included for Design Guidance and are not subject

to production testing.)

AC PERFORMANCE CHARACTERISTICS

A & B

Versions

Parameter

Units

Test Conditions/Comments

DYNAMIC PERFORMANCE

Output Voltage Settling Time

31

μ

s typ

Full-Scale Change to

±

1/2 LSB. DAC Latch Contents Alternately

Loaded with All 0s and All 1s

Slew Rate

Digital-to-Analog Glitch Impulse

0.7

230

V/

μ

s typ

nV-s typ

Measured with V

REF

(+) = +5 V, V

REF

(–) = –5 V. DAC Latch

Alternately Loaded with 1FFF Hex and 2000 Hex. Not Dependent

on Load Conditions

See Terminology

See Terminology

Feedthrough to DAC Output Under Test Due to Change in Digital

Input Code to Another Converter

Effect of Input Bus Activity on DAC Output Under Test

Channel-to-Channel Isolation

DAC-to-DAC Crosstalk

Digital Crosstalk

99

40

0.2

dB typ

nV-s typ

nV-s typ

Digital Feedthrough

Output Noise Spectral Density

@ 1 kHz

0.1

nV-s typ

200

nV/

√

Hz

typ

All 1s Loaded to DAC. V

REF

(+) = V

REF

(–) = 0 V

TIMING SPECIFICATIONS

1, 2

Parameter

Limit at T

MIN,

T

MAX

Units

Description

t

1

t

2

t

3

t

4

t

5

t

6

t

7

t

8

t

9

t

10

t

11

15

0

50

50

0

0

20

0

31

300

50

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min

μ

s typ

ns max

ns min

Address to

WR

Setup Time

Address to

WR

Hold Time

CS

Pulsewidth Low

WR

Pulsewidth Low

CS

to

WR

Setup Time

WR

to

CS

Hold Time

Data Setup Time

Data Hold Time

Settling Time

CLR

Pulse Activation Time

LDAC

Pulsewidth Low

NOTES

1

All input signals are specified with tr = tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

2

Rise and fall times should be no longer than 50 ns.

Specifications subject to change without notice.

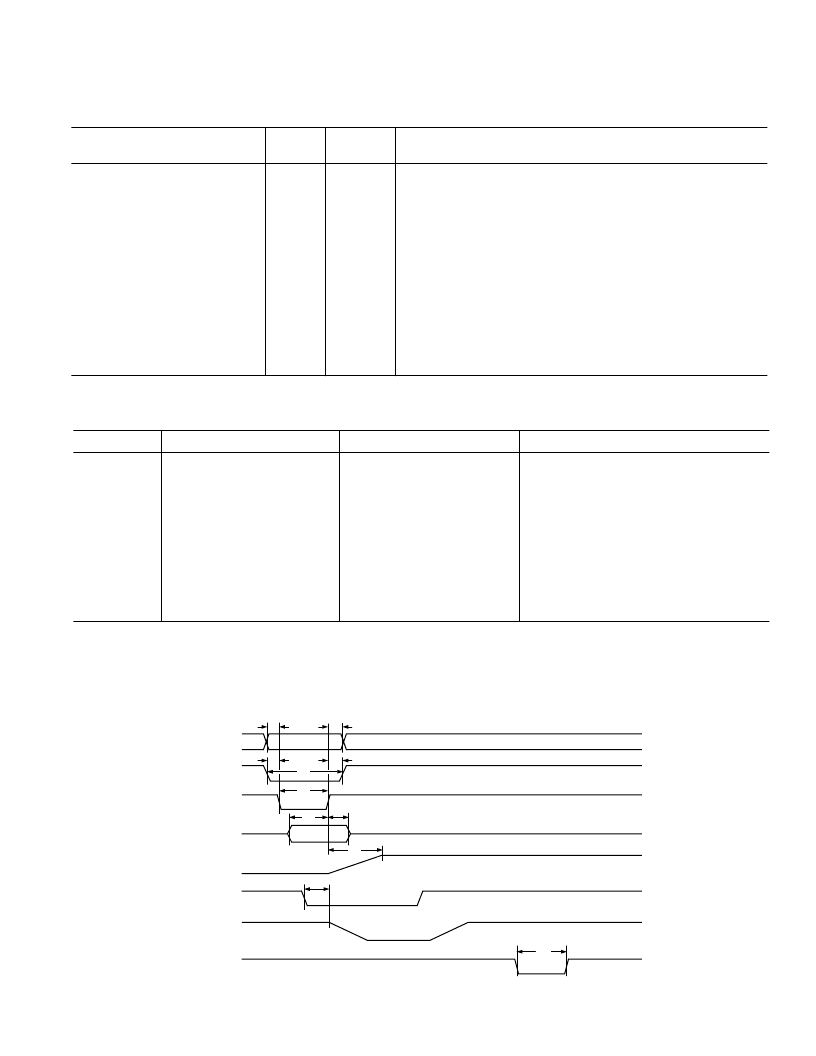

t

1

t

2

t

5

t

6

t

3

t

4

t

7

t

8

t

9

t

10

t

11

LDAC

CLR

WR

CS

A0, A1, A2

DATA

V

OUT

V

OUT

Figure 1. Timing Diagram

(V

CC

= +5 V

6

5%; V

DD

= +15 V

6

10%; V

SS

= –15 V

6

10%; GND = DUTGND = 0 V)

相關PDF資料 |

PDF描述 |

|---|---|

| AD7841AS | Octal 14-Bit, Parallel Input, Voltage-Output DAC |

| AD7841BS | Octal 14-Bit, Parallel Input, Voltage-Output DAC |

| AD7843ARU-REEL | Touch Screen Digitizer |

| AD7843 | Touch Screen Digitizer |

| AD7843ARQ | Touch Screen Digitizer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7841AS | 制造商:Analog Devices 功能描述:DAC 8-CH R-2R 14-bit 44-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:OCTAL 14-BIT HIGH VOLTAGE DAC I.C. - Bulk 制造商:Analog Devices 功能描述:Digital/Analog Converter IC Interface Ty |

| AD7841AS-REEL | 制造商:Analog Devices 功能描述:DAC 8-CH R-2R 14-bit 44-Pin MQFP T/R |

| AD7841ASZ | 功能描述:IC DAC 14BIT OCTAL V-OUT 44MQFP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 數模轉換器 系列:- 標準包裝:1 系列:- 設置時間:4.5µs 位數:12 數據接口:串行,SPI? 轉換器數目:1 電壓電源:單電源 功率耗散(最大):- 工作溫度:-40°C ~ 125°C 安裝類型:表面貼裝 封裝/外殼:8-SOIC(0.154",3.90mm 寬) 供應商設備封裝:8-SOICN 包裝:剪切帶 (CT) 輸出數目和類型:1 電壓,單極;1 電壓,雙極 采樣率(每秒):* 其它名稱:MCP4921T-E/SNCTMCP4921T-E/SNRCTMCP4921T-E/SNRCT-ND |

| AD7841ASZ-REEL | 功能描述:IC DAC 14BIT OCTAL VOUT 44-MQFP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 數模轉換器 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1,000 系列:- 設置時間:1µs 位數:8 數據接口:串行 轉換器數目:8 電壓電源:雙 ± 功率耗散(最大):941mW 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應商設備封裝:24-SOIC W 包裝:帶卷 (TR) 輸出數目和類型:8 電壓,單極 采樣率(每秒):* |

| AD7841BS | 制造商:Analog Devices 功能描述:DAC 8-CH R-2R 14-bit 44-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:OCTAL 14 BIT HIGH VOLTAGE IC - Bulk 制造商:Analog Devices 功能描述:Digital-Analog Converter IC Interface Ty |

發布緊急采購,3分鐘左右您將得到回復。