- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373920 > AD7862ARS-10 (ANALOG DEVICES INC) Simultaneous Sampling Dual 250 kSPS 12-Bit ADC PDF資料下載

參數(shù)資料

| 型號: | AD7862ARS-10 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | Simultaneous Sampling Dual 250 kSPS 12-Bit ADC |

| 中文描述: | 2-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO28 |

| 封裝: | SSOP-28 |

| 文件頁數(shù): | 10/16頁 |

| 文件大小: | 414K |

| 代理商: | AD7862ARS-10 |

AD7862

–10–

REV. 0

respectively). The third and fourth read pulses, after the second

conversion and A0 high, access the result from Channel B (V

B1

and V

B2

respectively). Data is read from the part via a 12-bit

parallel data bus with standard

CS

and

RD

signals. This data

read operation consists of negative going pulse on the

CS

pin

combined with a negative going pulse on the

RD

pin; this repeated

twice will access the two 12-bit results. For the fastest throughput

rate (with an internal clock of 3.7 MHz), the read operation will

take 100 ns. The read operation must be complete at least 300 ns

before the falling edge of the next

CONVST

, and this gives a total

time of 4

μ

s for the full throughput time (equivalent to 250kHz).

This mode of operation should be used for high sampling

applications.

Mode 2 Operation (Auto Sleep After Conversion)

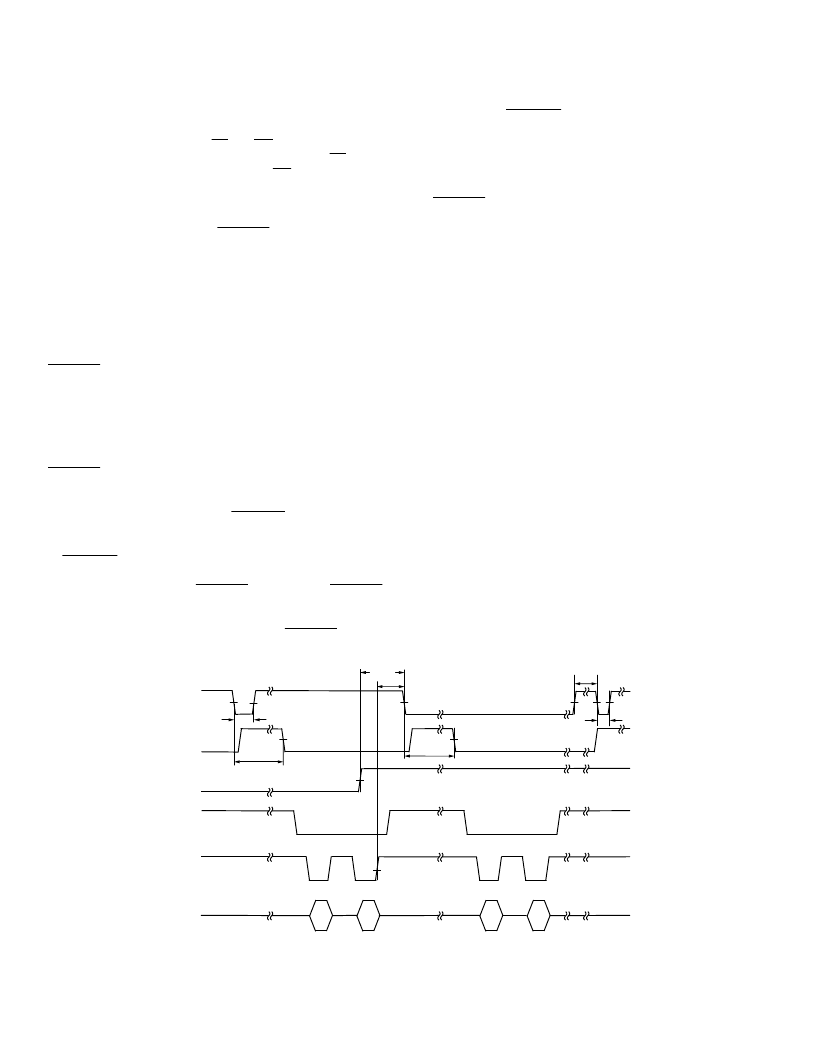

The timing diagram in Figure 6 is for optimum performance in

Operating Mode 2 where the part automatically goes into sleep

mode once BUSY goes low after conversion and “wakes-up”

before the next conversion takes place. This is achieved by keeping

CONVST

low at the end of the second conversion, whereas it

was high at the end of the second conversion for Mode 1 opera-

tion. The operation shown in Figure 6 shows how to access data

from both Channels A and B followed by the Auto Sleep mode.

One can also setup the timing to access data from Channel A

only or Channel B only (see

Read Options

section on previous

page) and then go into Auto-Sleep mode. The rising edge of

CONVST

“wakes-up” the part. This wake-up time is 2.5

μ

s

when using an external reference and 5 ms when using the

internal reference at which point the Track/Hold amplifier’s go

into their hold mode, provided the

CONVST

has gone low. The

conversion takes 3.6

μ

s after this, giving a total of 6

μ

s (external

reference, 5.0035 ms for internal reference) from the rising edge

of

CONVST

to the conversion being complete, which is

indicated by the BUSY going low. Note that since the wake-up

time from the rising edge of

CONVST

is 2.5

μ

s, if the

CONVST

pulse width is greater than 2.5

μ

s, the conversion will take more

than the 6

μ

s (2.5

μ

s wake-up time + 3.6

μ

s conversion time)

shown in the diagram from the rising edge of

CONVST

. This is

because the track/hold amplifiers go into their hold mode on

the falling edge of

CONVST

, and the conversion will not be

complete for a further 3.6

μ

s. In this case the BUSY will be the

best indicator for when the conversion is complete. Even though

the part is in sleep mode, data can still be read from the part.

The read operation is identical to Mode 1 operation and must

also be complete at least 300 ns before the falling edge of the

next

CONVST

to allow the track/hold amplifiers to have enough

time to settle. This mode is very useful when the part is convert-

ing at a slow rate, as the power consumption will be significantly

reduced from that of Mode 1 operation.

DYNAMIC SPECIFICATIONS

The AD7862 is specified and 100% tested for dynamic perfor-

mance specifications as well as traditional dc specifications such

as Integral and Differential Nonlinearity. These ac specifications

are required for the signal processing applications such as phased

array sonar, adaptive filters and spectrum analysis. These applica-

tions require information on the ADC’s effect on the spectral

content of the input signal. Hence, the parameters for which the

AD7862 is specified include SNR, harmonic distortion, inter-

modulation distortion and peak harmonics. These terms are

discussed in more detail in the following sections.

Signal-to-Noise Ratio (SNR)

SNR is the measured signal-to-noise ratio at the output of the

ADC. The signal is the rms magnitude of the fundamental.

Noise is the rms sum of all the nonfundamental signals up to

half the sampling frequency (f

S

/2) excluding dc. SNR is depen-

dent upon the number of quantization levels used in the

digitization process; the more levels, the smaller the quantiza-

tion noise. The theoretical signal to noise ratio for a sine wave

input is given by

SNR

= (6.02

N

+ 1.76)

dB

where

N

is the number of bits.

Thus for an ideal 12-bit converter, SNR = 74 dB.

(1)

V

A1

V

A2

V

B1

V

B2

t

3

t

CONV

= 3.6μs

CONVST

BUSY

A0

CS

RD

DATA

300ns

400ns

t

3

2.5μs*/5ms**

WAKE-UP

TIME

t

CONV

= 3.5μs

*

*WHEN USING AN EXTERNAL REFERENCE, WAKE-UP TIME = 2.5μs

**WHEN USING AN INTERNAL REFERENCE, WAKE-UP TIME = 5ms

Figure 6. Mode 2 Timing Where Automatic Sleep Function Is Initiated

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7862ARS-2 | Simultaneous Sampling Dual 250 kSPS 12-Bit ADC |

| AD7862ARS-3 | Simultaneous Sampling Dual 250 kSPS 12-Bit ADC |

| AD7862BR-3 | Simultaneous Sampling Dual 250 kSPS 12-Bit ADC |

| AD7862AN-10 | Simultaneous Sampling Dual 250 kSPS 12-Bit ADC |

| AD7862AN-3 | Simultaneous Sampling Dual 250 kSPS 12-Bit ADC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7862ARS-10REEL | 功能描述:IC ADC 12BIT DUAL 250KSPS 28SSOP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標準包裝:1,000 系列:- 位數(shù):12 采樣率(每秒):300k 數(shù)據(jù)接口:并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):75mW 電壓電源:單電源 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應商設備封裝:24-SOIC 包裝:帶卷 (TR) 輸入數(shù)目和類型:1 個單端,單極;1 個單端,雙極 |

| AD7862ARS-10Z | 制造商:Analog Devices 功能描述:ADC DUAL 12BIT 250KSPS 28S 制造商:Analog Devices 功能描述:ADC, DUAL, 12BIT, 250KSPS, 28SSOP; Resolution (Bits):12bit; Sampling Rate:250kSPS; Supply Voltage Type:Single; Supply Voltage Min:4.75V; Supply Voltage Max:5.25V; Supply Current:15mA; Digital IC Case Style:SSOP; No. of Pins:28; Input;RoHS Compliant: Yes |

| AD7862ARS-2 | 功能描述:IC ADC 12BIT DUAL 250KSPS 28SSOP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標準包裝:1 系列:- 位數(shù):14 采樣率(每秒):83k 數(shù)據(jù)接口:串行,并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數(shù)目和類型:1 個單端,雙極 |

| AD7862ARS-2REEL | 功能描述:IC ADC 12BIT DUAL 250KSPS 28SSOP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標準包裝:1,000 系列:- 位數(shù):12 采樣率(每秒):300k 數(shù)據(jù)接口:并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):75mW 電壓電源:單電源 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應商設備封裝:24-SOIC 包裝:帶卷 (TR) 輸入數(shù)目和類型:1 個單端,單極;1 個單端,雙極 |

| AD7862ARS-3 | 功能描述:IC ADC 12BIT DUAL 250KSPS 28SSOP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標準包裝:1 系列:- 位數(shù):14 采樣率(每秒):83k 數(shù)據(jù)接口:串行,并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數(shù)目和類型:1 個單端,雙極 |

發(fā)布緊急采購,3分鐘左右您將得到回復。