- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373921 > AD7863BR-10 (ANALOG DEVICES INC) RECTIFIER FAST-RECOVERY SINGLE 1A 400V 30A-ifsm 1.3V-vf 50ns 5uA-ir DO-41 1K/BULK PDF資料下載

參數(shù)資料

| 型號(hào): | AD7863BR-10 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | RECTIFIER FAST-RECOVERY SINGLE 1A 400V 30A-ifsm 1.3V-vf 50ns 5uA-ir DO-41 1K/BULK |

| 中文描述: | 4-CH 14-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO28 |

| 封裝: | MS-013AE, SOIC-28 |

| 文件頁數(shù): | 14/18頁 |

| 文件大小: | 207K |

| 代理商: | AD7863BR-10 |

AD7863

–

14

–

REV. A

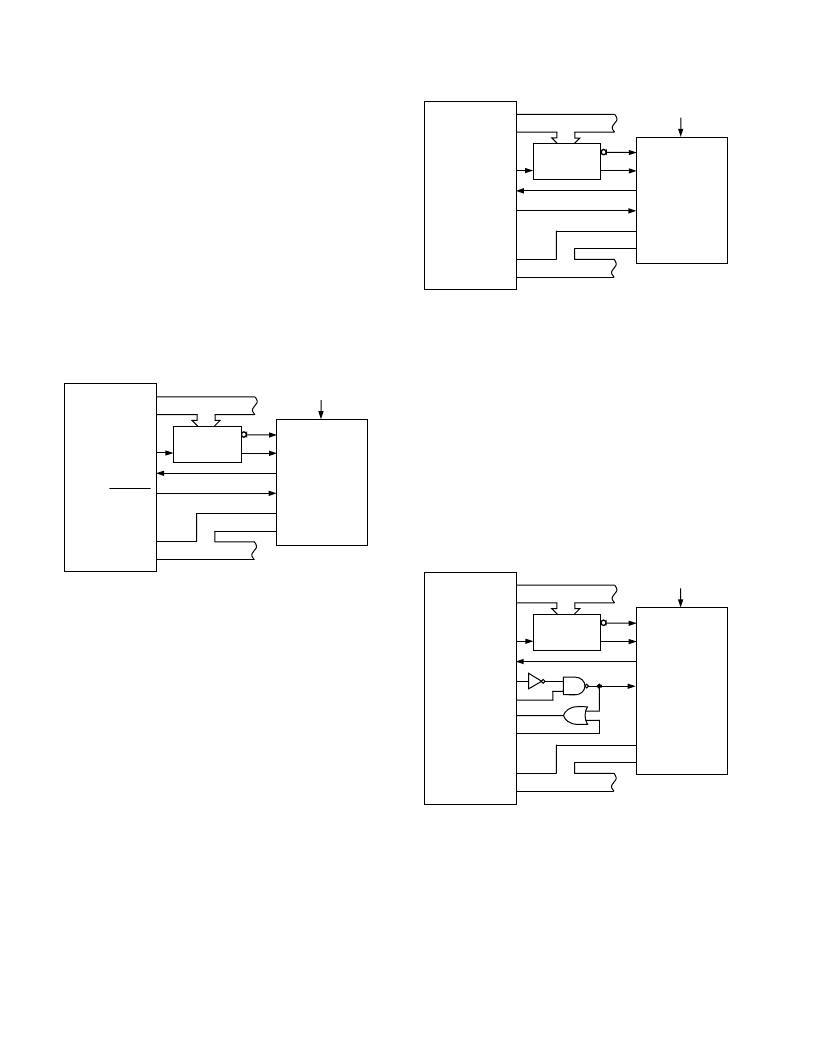

MICROPROCESSOR INTERFACING

The AD7863 high speed bus timing allows direct interfacing to

DSP processors as well as modern 16-bit microprocessors.

Suitable microprocessor interfaces are shown in Figures 14

through 18.

AD7863–ADSP-2100 Interface

Figure 14 shows an interface between the AD7863 and the

ADSP-2100. The

CONVST

signal can be supplied from the

ADSP-2100 or from an external source. The AD7863 BUSY

line provides an interrupt to the ADSP-2100 when conversion is

completed on both channels. The two conversion results can

then be read from the AD7863 using two successive reads to the

same memory address. The following instruction reads one of

the two results:

MR

0 =

DM

(

ADC

)

where

MR

0 is the ADSP-2100

MR

0 register and

ADC

is the

AD7863 address.

ADDR

DECODE

EN

ADDRESS BUS

DMA13

DMA0

DMS

IRQn

DMRD (RD)

DMD15

DMD0

CS

A0

BUSY

RD

DB13

DB0

DATA BUS

ADSP-2100

(ADSP-2101/

ADSP-2102)

AD7863*

*ADDITIONAL PINS OMITTED FOR CLARITY

OPTIONAL

CONVST

Figure 14. AD7863

–

ADSP-2100 Interface

AD7863–ADSP-2101/ADSP-2102 Interface

The interface outlined in Figure 14 also forms the basis for an

interface between the AD7863 and the ADSP-2101/ADSP-2102.

The READ line of the ADSP-2101/ADSP-2102 is labeled

RD

.

In this interface, the

RD

pulsewidth of the processor can be

programmed using the Data Memory Wait State Control Regis-

ter. The instruction used to read one of the two results is as

outlined for the ADSP-2100.

AD7863–TMS32010 Interface

An interface between the AD7863 and the TMS32010 is

shown in Figure 15. Once again the

CONVST

signal can be

supplied from the TMS32010 or from an external source,

and the TMS32010 is interrupted when both conversions have

been completed. The following instruction is used to read the

conversion results from the AD7863:

IN D

,

ADC

where

D

is Data Memory address and

ADC

is the AD7863

address.

ADDR

DECODE

EN

ADDRESS BUS

PA2

PA0

MEN

INT

DEN

D15

D0

CS

A0

BUSY

RD

DB13

DB0

DATA BUS

TMS32010

AD7863*

*ADDITIONAL PINS OMITTED FOR CLARITY

OPTIONAL

CONVST

Figure 15. AD7863

–

TMS32010 Interface

AD7863–TMS320C25 Interface

Figure 16 shows an interface between the AD7863 and the

TMS320C25. As with the two previous interfaces, conversion

can be initiated from the TMS320C25 or from an external

source, and the processor is interrupted when the conversion

sequence is completed. The TMS320C25 does not have a sepa-

rate

RD

output to drive the AD7863

RD

input directly. This

has to be generated from the processor STRB and R/

W

outputs

with the addition of some logic gates. The

RD

signal is OR-

gated with the

MSC

signal to provide the one WAIT state re-

quired in the read cycle for correct interface timing. Conversion

results are read from the AD7863 using the following instruction:

IN D

,

ADC

where

D

is Data Memory address and

ADC

is the AD7863

address.

ADDR

DECODE

EN

ADDRESS BUS

A15

A0

IS

INTn

STRB

DMD15

DMD0

CS

A0

BUSY

RD

DB13

DB0

DATA BUS

TMS320C25

AD7863*

*ADDITIONAL PINS OMITTED FOR CLARITY

OPTIONAL

CONVST

R/

W

READY

MSC

Figure 16. AD7863

–

TMS320C25 Interface

Some applications may require that the conversion is initiated

by the microprocessor rather than an external timer. One option

is to decode the AD7863

CONVST

from the address bus so

that a write operation starts a conversion. Data is read at the

end of the conversion sequence as before. Figure 18 shows an

example of initiating conversion using this method. Note that

for all interfaces, it is preferred that a read operation not be

attempted during conversion.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7863BR-3 | RECTIFIER FAST-RECOVERY SINGLE 1A 600V 30A-ifsm 1.7V-vf 75ns 5uA-ir DO-41 1K/BULK |

| AD7863ARS-10 | Simultaneous Sampling Dual 175 kSPS 14-Bit ADC |

| AD7863ARS-2 | Simultaneous Sampling Dual 175 kSPS 14-Bit ADC |

| AD7863ARS-3 | Simultaneous Sampling Dual 175 kSPS 14-Bit ADC |

| AD7863AR-2 | RECTIFIER SCHOTTKY DUAL 30A 60V 275A-ifsm 0.7V-vf 1mA-ir TO-3P 30/TUBE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7863BR-10REEL | 制造商:Analog Devices 功能描述:ADC Dual SAR 175ksps 14-bit Parallel 28-Pin SOIC W T/R 制造商:Rochester Electronics LLC 功能描述:2 CH.SIMULTANEOUS SAMPL.14-B DUAL ADC IC - Tape and Reel |

| AD7863BR-10REEL7 | 制造商:Analog Devices 功能描述:ADC Dual SAR 175ksps 14-bit Parallel 28-Pin SOIC W T/R |

| AD7863BR-3 | 功能描述:IC ADC 14BIT DUAL 2CH 28-SOIC RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 位數(shù):14 采樣率(每秒):83k 數(shù)據(jù)接口:串行,并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應(yīng)商設(shè)備封裝:28-PDIP 包裝:管件 輸入數(shù)目和類型:1 個(gè)單端,雙極 |

| AD7863BR-3REEL | 功能描述:IC ADC 14BIT DUAL 2CH 28-SOIC RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 位數(shù):14 采樣率(每秒):83k 數(shù)據(jù)接口:串行,并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應(yīng)商設(shè)備封裝:28-PDIP 包裝:管件 輸入數(shù)目和類型:1 個(gè)單端,雙極 |

| AD7863BR-3REEL7 | 功能描述:IC ADC 14BIT DUAL 2CH 28-SOIC RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:- 位數(shù):12 采樣率(每秒):3M 數(shù)據(jù)接口:- 轉(zhuǎn)換器數(shù)目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應(yīng)商設(shè)備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數(shù)目和類型:- |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。