- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373921 > AD7864AS-1 (ANALOG DEVICES INC) VARISTOR 150V RMS 20MM RADIAL PDF資料下載

參數(shù)資料

| 型號: | AD7864AS-1 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | VARISTOR 150V RMS 20MM RADIAL |

| 中文描述: | 4-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PQFP44 |

| 封裝: | PLASTIC, MO-112-AA, MQFP-44 |

| 文件頁數(shù): | 11/19頁 |

| 文件大小: | 214K |

| 代理商: | AD7864AS-1 |

AD7864

–11–

REV. A

TIMING AND CONTROL

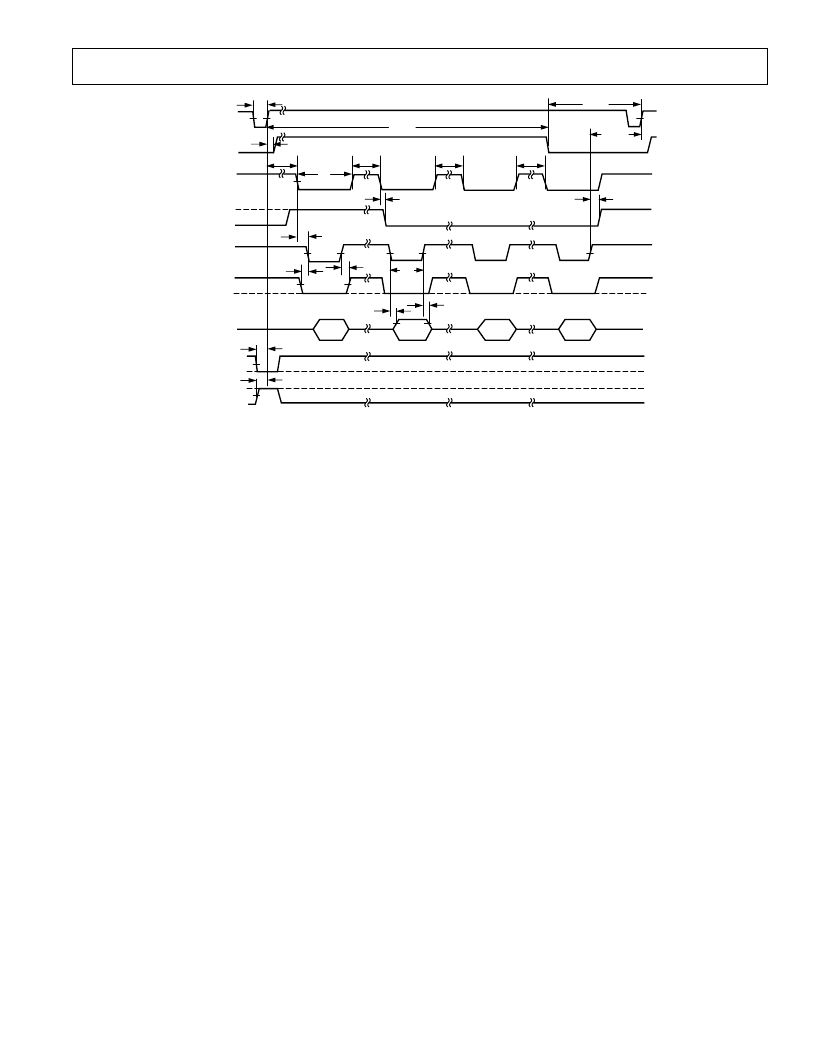

Reading Between Each Conversion in the Conversion Sequence

Figure 7 shows the timing and control sequence required to

obtain the optimum throughput rate from the AD7864. To

obtain the optimum throughput from the AD7864 the user must

read the result of each conversion as it becomes available. The

timing diagram in Figure 7 shows a read operation each time the

EOC

signal goes logic low. The timing in Figure 7 shows a

conversion on all four analog channels (SL1 to SL4 = 1, see

Channel Selection), hence there are four

EOC

pulses and four read

operations to access the result of each of the four conversions.

A conversion is initiated on the rising edge of

CONVST

. This

places all four track/holds into hold simultaneously. New data

from this conversion sequence is available for the first channel

selected (V

IN1

) 1.65

μ

s later. The conversion on each subse-

quent channel is completed at 1.65

μ

s intervals. The end of each

conversion is indicated by the falling edge of the

EOC

signal.

The BUSY output signal indicates the end of conversion for all

selected channels (four in this case).

Data is read from the part via a 12-bit parallel data bus with

standard

CS

and

RD

signals. The

CS

and

RD

inputs are inter-

nally gated to enable the conversion result onto the data bus.

The data lines DB0 to DB11 leave their high impedance state

when both

CS

and

RD

are logic low. Therefore,

CS

may be

permanently tied logic low and the

RD

signal used to access the

conversion result. Since each conversion result is latched into its

output data register prior to

EOC

going logic low a further

option would be to tie the

EOC

and

RD

pins together and use

the rising edge of

EOC

to latch the conversion result. Although

the AD7864 has some special features that permit reading dur-

ing a conversion (e.g., a separate supply for the output data

drivers, V

DRIVE

), for optimum performance it is recommended

that the read operation be completed when

EOC

is logic low,

i.e., before the start of the next conversion. Although Figure 8

shows the read operation taking place during the

EOC

pulse, a

read operation can take place at any time. Figure 8 shows a

timing specification called “Quiet Time.” This is the amount of

time that should be left after a read operation and before the

next conversion is initiated. The quiet time depends heavily on

data bus capacitance but a figure of 50 ns to 100 ns is typical.

The signal labeled FRSTDATA (First Data Word) indicates to

the user that the pointer associated with the output data regis-

ters is pointing to the first conversion result by going logic high.

The pointer is reset to point to the first data location (i.e., first

conversion result,) at the end of the first conversion (FRSTDATA

logic high). The pointer is incremented to point to the next

register (next conversion result) when that conversion result is

available. Hence, FRSTDATA in Figure 7 is seen to go low just

prior to the second

EOC

pulse. Repeated read operations dur-

ing a conversion will continue to access the data at the current

pointer location until the pointer is incremented at the end of that

conversion. Note FRSTDATA has an indeterminate logic state

after initial power up. This means that for the first conversion

sequence after power up, the FRSTDATA logic output may

already be logic high before the end of the first conversion. This

condition is indicated by the dashed line in Figure 7. Also the

FRSTDATA logic output may already be high as a result of the

previous read sequence as is the case after the fourth read in

Figure 7. The fourth read (rising edge of

RD

) resets the

pointer to the first data location. Therefore, FRSTDATA is

already high when the next conversion sequence is initiated.

See Accessing the Output Data Registers.

t

CONV

t

BUSY

QUIET

TIME

t

1

t

8

t

11

t

3

t

4

t

5

t

6

t

7

V

IN1

V

IN2

V

IN3

V

IN4

100ns

100ns

DATA

CONVST

BUSY

EOC

FRSTDATA

RD

CS

H

/S SEL

SL1–SL4

t

2

t

CONV

t

CONV

t

CONV

t

ACQ

t

11

t

10

Figure 7. Timing Diagram for Reading During Conversion

相關PDF資料 |

PDF描述 |

|---|---|

| AD7864BS-1 | SWITCH SLIDE DP3T RT ANG L=6MM |

| AD7864AS-2 | 4-Channel, Simultaneous Sampling, High Speed, 12-Bit ADC |

| AD7864AS-3 | 4-Channel, Simultaneous Sampling, High Speed, 12-Bit ADC |

| AD7864AS | IC-SM-12-BIT ADC |

| AD7865YS-1 | Four-Channel, Simultaneous Sampling, Fast, 14-Bit ADC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AD7864AS-2 | 制造商:Analog Devices 功能描述:ADC Single SAR 520ksps 12-bit Parallel 44-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:4 CH.SIMULTANEOUS SAMPL.500 KSPS ADC I.C - Bulk 制造商:Analog Devices 功能描述:IC 12-BIT ADC |

| AD7864AS-2REEL | 制造商:Analog Devices 功能描述:ADC Single SAR 520ksps 12-bit Parallel 44-Pin MQFP T/R |

| AD7864AS-2Z | 制造商:Analog Devices 功能描述:ADC 12BIT 4CH 500KSPS 44MQ 制造商:Analog Devices 功能描述:ADC, 12BIT, 4CH, 500KSPS, 44MQFP; Resolution (Bits):12bit; Sampling Rate:520kSPS; Supply Voltage Type:Single; Supply Voltage Min:4.75V; Supply Voltage Max:5.25V; Supply Current:24mA; Digital IC Case Style:MQFP; No. of Pins:44; Input ;RoHS Compliant: Yes |

| AD7864AS-3 | 制造商:Analog Devices 功能描述:ADC Single SAR 520ksps 12-bit Parallel 44-Pin MQFP 制造商:Analog Devices 功能描述:IC 12-BIT ADC |

| AD7864AS-3REEL | 制造商:Analog Devices 功能描述:ADC Single SAR 520ksps 12-bit Parallel 44-Pin MQFP T/R |

發(fā)布緊急采購,3分鐘左右您將得到回復。