- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373922 > AD7871 (Analog Devices, Inc.) LC2MOS Complete 14-Bit, Sampling ADCs PDF資料下載

參數(shù)資料

| 型號(hào): | AD7871 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | LC2MOS Complete 14-Bit, Sampling ADCs |

| 中文描述: | LC2MOS完整的14位,采樣ADC |

| 文件頁(yè)數(shù): | 8/16頁(yè) |

| 文件大小: | 344K |

| 代理商: | AD7871 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

AD7871/AD7872

–8–

REV. D

placed on the data bus. T hese six bits are right justified and

thereby occupy the lower six bits of the byte while the upper two

bits are zeros.

Serial Output Format

Serial data is available on the AD7871 when the 14/

8

/CLK

input is at 0 V or –5 V and in this case the DB12/

SSTRB

,

DB11/SCLK and DB10/SDAT A pins assume their serial func-

tions. T he AD7872 is a serial output device only. T he serial

function on both devices is identical. Serial data is available dur-

ing conversion with a word length of 16 bits; two leading zeros,

followed by the 14-bit conversion result starting with the MSB.

T he data is synchronized to the serial clock output (SCLK ) and

is framed by the serial strobe (

SSTRB

). Data is clocked out on a

low to high transition of the serial clock and is valid on the fall-

ing edge of this clock while the

SSTRB

output is low.

SSTRB

goes low at the start of conversion and the first serial data bit

(which is the first leading zero) is valid on the first falling edge

of SCLK . All the serial lines are open-drain outputs and require

external pull-up resistors.

T he serial clock out is derived from the ADC master clock

source which may be internal or external. Normally, SCLK is

required during the serial transmission only. In these cases it

can be shut down (i.e., placed into three-state) at the end of

conversion to allow multiple ADCs to share a common serial

bus. However, some serial systems (e.g., T MS32020) require a

serial clock that runs continuously. Both options are available

on the AD7871 and AD7872. With the 14/

8

/CLK input on the

AD7871 at –5 V, the serial clock (SCLK ) runs continuously;

when 14/

8

/CLK is at 0 V, SCLK goes into three-state at the end

of transmission. T he CONT ROL pin on the AD7872 performs

the same function. When this is at 0 V, SCLK is noncontinuous

and when it is at –5 V, SCLK is continuous.

T he SCLK , SDAT A and

SSTRB

lines are open-drain outputs.

If these are required to drive capacitive loads in excess of 35 pF,

buffering is recommended.

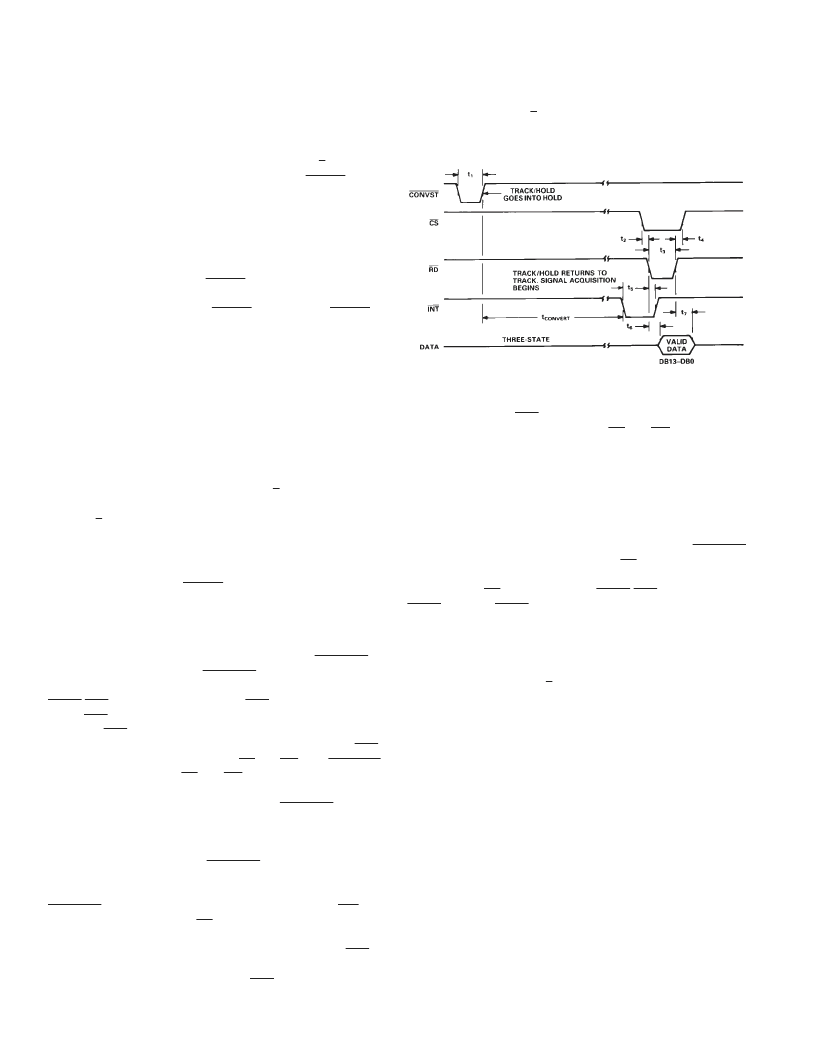

MODE 1 INT E RFACE

Conversion is initiated by a low going pulse on the

CONVST

input. T he rising edge of this

CONVST

pulse starts conversion

and drives the track/hold amplifier into its hold mode. T he

BUSY

/

INT

status output assumes its

INT

function in this

mode.

INT

is normally high and goes low at the end of conver-

sion. T his

INT

line can be used to interrupt the microprocessor.

A read operation to the AD7871 accesses the data and the

INT

line is reset high on the falling edge of

CS

and

RD

. T he

CONVST

input must be high when

CS

and

RD

are brought low for the

AD7871 to operate correctly in this mode. It is important, espe-

cially in systems where the conversion start (

CONVST

) pulse is

asynchronous to the microprocessor, to ensure that a parallel or

byte data read is not attempted during a conversion. T rying to

read data during a conversion can cause errors to the conversion

in progress. Avoid pulsing the

CONVST

line a second time be-

fore conversion end since it can cause errors in the conversion

result. In applications where precise sampling is not critical, the

CONVST

pulse can be generated from microprocessor

WR

line

OR-gated with the AD7871

CS

input. In some applications, de-

pending on power supply turn-on time, the AD7871/AD7872

may perform a conversion on power-up. In this case, the

INT

line on the AD7871 will power up low, and a dummy read to

the device will be required to reset the

INT

line before starting

conversion.

Figure 9 shows the Mode 1 timing diagram for a 14-bit parallel

data output format (14/

8

/CLK = +5 V). A read to the AD7871

at the end of conversion accesses all 14 bits of data at the same

time. Serial data is not available for this data output format.

Figure 9. Mode 1 Timing Diagram, 14-Bit Parallel Read

T he Mode 1 function timing diagram for byte and serial data is

shown in Figure 10.

INT

goes low at the end of conversion and

is reset high by the first falling edge of

CS

and

RD

. T his first

read at the end of conversion can either access the low byte or

high byte of data depending on the status of HBEN (Figure 10

shows low byte for example only). T he diagram shows both the

SCLK output going into three-state at the end of transmission

and a continuously running clock (dashed line).

MODE 2 INT E RFACE

T he second interface mode is achieved by hard-wiring

CONVST

low and conversion is initiated by taking

CS

low while HBEN is

low. T he track/hold amplifier goes into the hold mode on the

falling edge of

CS

. In this mode the

BUSY

/

INT

pin assumes its

BUSY

function.

BUSY

goes low at the start of conversion, stays

low during the conversion and returns high when the conversion

is complete. It is normally used in parallel interfaces to drive the

microprocessor into a WAIT state for the duration of conversion.

Figure 11 shows the Mode 2 timing diagram for the 14-bit paral-

lel data output format (14/

8

/CLK = +5 V). In this case the ADC

behaves like slow memory. T he major advantage of this interface

is that it allows the microprocessor to start conversion, WAIT

and then read data with a single READ instruction. T he user

does not have to worry about servicing interrupts or ensuring

that software delays are long enough to avoid the reading during

conversion.

T he Mode 2 timing diagram for byte and serial data is shown in

Figure 12. For 2-byte data read, the lower byte (DB0–DB7) has

to be accessed first since HBEN must be low to start con-ver-

sion. T he ADC behaves like slow memory for this first read, but

the second read to access the upper byte of data is a normal read.

Operation to the serial functions is identical between Mode 1

and Mode 2. Once again, the timing diagram of Figure 12 shows

SCLK going into three-state or running continuously (dashed

line).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7871JP | LC2MOS Complete 14-Bit, Sampling ADCs |

| AD7871KN | 10-Bit, 20 MSPS ADC SE/Diff Inputs with Int References and 9.5 bit ENOB 28-SOIC -40 to 85 |

| AD7871KP | LC2MOS Complete 14-Bit, Sampling ADCs |

| AD7871TQ | LC2MOS Complete 14-Bit, Sampling ADCs |

| AD7872 | LC2MOS Complete 14-Bit, Sampling ADCs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7871AQ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog-to-Digital Converter, 14-Bit |

| AD7871BQ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog-to-Digital Converter, 14-Bit |

| AD7871JN | 功能描述:IC ADC 14BIT SAMPLING 28-DIP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 位數(shù):14 采樣率(每秒):83k 數(shù)據(jù)接口:串行,并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應(yīng)商設(shè)備封裝:28-PDIP 包裝:管件 輸入數(shù)目和類型:1 個(gè)單端,雙極 |

| AD7871JNZ | 功能描述:IC ADC 14BIT SAMPLING 28-DIP RoHS:是 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 其它有關(guān)文件:TSA1204 View All Specifications 標(biāo)準(zhǔn)包裝:1 系列:- 位數(shù):12 采樣率(每秒):20M 數(shù)據(jù)接口:并聯(lián) 轉(zhuǎn)換器數(shù)目:2 功率耗散(最大):155mW 電壓電源:模擬和數(shù)字 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-TQFP 供應(yīng)商設(shè)備封裝:48-TQFP(7x7) 包裝:Digi-Reel® 輸入數(shù)目和類型:4 個(gè)單端,單極;2 個(gè)差分,單極 產(chǎn)品目錄頁(yè)面:1156 (CN2011-ZH PDF) 其它名稱:497-5435-6 |

| AD7871JP | 功能描述:IC ADC 14BIT SAMPLING 28-PLCC RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:- 位數(shù):12 采樣率(每秒):3M 數(shù)據(jù)接口:- 轉(zhuǎn)換器數(shù)目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應(yīng)商設(shè)備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數(shù)目和類型:- |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。