- 您現在的位置:買賣IC網 > PDF目錄373922 > AD7872 (Analog Devices, Inc.) LC2MOS Complete 14-Bit, Sampling ADCs PDF資料下載

參數資料

| 型號: | AD7872 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | LC2MOS Complete 14-Bit, Sampling ADCs |

| 中文描述: | LC2MOS完整的14位,采樣ADC |

| 文件頁數: | 3/16頁 |

| 文件大小: | 344K |

| 代理商: | AD7872 |

AD7871/AD7872

–3–

REV. D

TIMNGCHARACTERISTICS

1, 2

Limit at T

MIN

, T

MAX

(J, K, A, B Versions)

Limit at T

MIN

, T

MAX

(T Version)

Parameter

Units

Conditions/Comments

t

1

t

2

t

3

t

4

t

5

t

63

t

74

50

0

60

0

70

57

5

50

0

0

100

440

155

140

20

4

100

60

120

200

0

0

0

50

0

75

0

70

70

5

50

0

0

100

440

155

150

20

4

100

60

120

200

0

0

0

ns min

ns min

ns min

ns min

ns min

ns max

ns min

ns max

ns min

ns min

ns min

ns min

ns max

ns max

ns min

ns min

ns max

ns min

ns max

ns min

ns min

ns min

ns min

CONVST

Pulse Width

CS

to

RD

Setup T ime (Mode 1)

RD

Pulse Width

CS

to

RD

Hold T ime (Mode 1)

RD

to

INT

Delay

Data Access T ime after

RD

Bus Relinquish T ime after

RD

t

8

t

9

t

t

10

t

126

t

13

HBEN to

RD

Setup T ime

HBEN to

RD

Hold T ime

SSTRB

to SCLK Falling

Edge Setup T ime

SCLK Cycle T ime

SCLK to Valid Data Delay. C

L

= 35 pF

SCLK Rising Edge to

SSTRB

t

14

Bus Relinquish T ime after SCLK

t

15

t

t

16

t

18

t

19

t

20

CS

to

RD

Setup T ime (Mode 2)

CS

to

BUSY

Propagation Delay

Data Setup T ime Prior to BUSY

CS

to

RD

Hold T ime (Mode 2)

HBEN to

CS

Setup T ime

HBEN to

CS

Hold T ime

NOT ES

1

T iming Specifications in

bold print

are 100% production tested. All other times are sample tested at +25

°

C to ensure compliance. All input signals are specified with

tr = tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

2

Serial timing is measured with a 4.7 k

pull-up resistor on SDAT A and

SSTRB

and a 2 k

pull-up resistor on SCLK . T he capacitance on all three outputs is 35 pF.

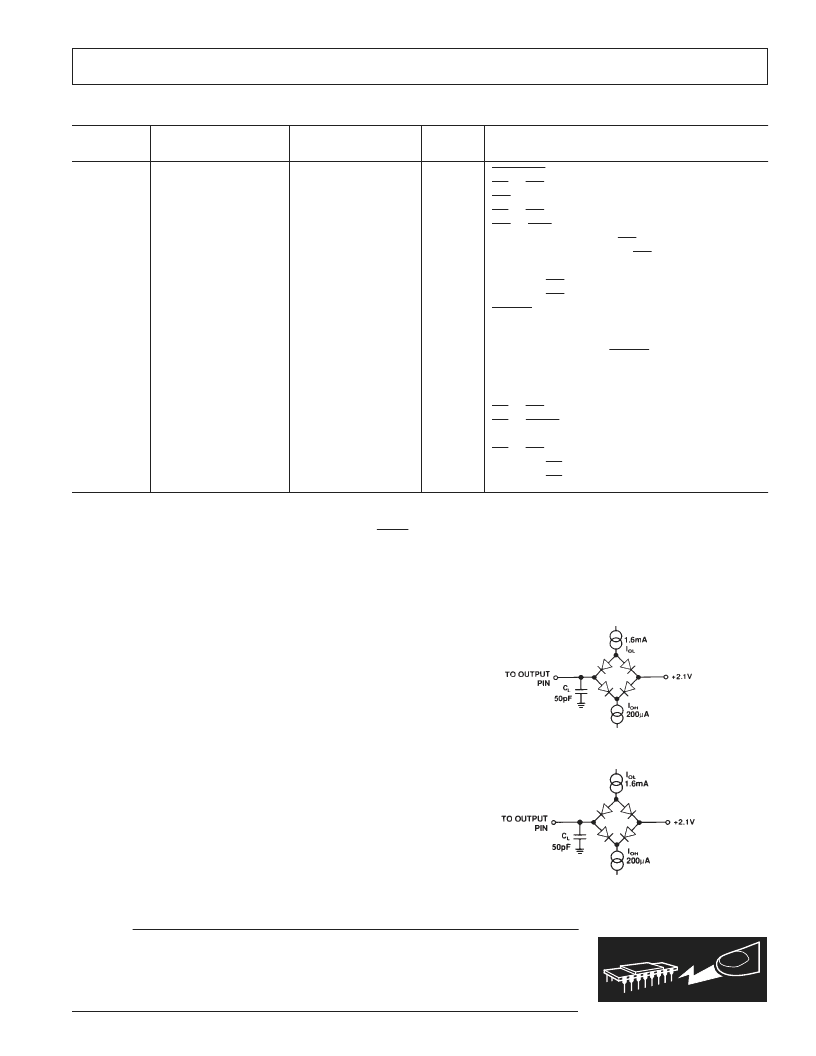

3

t

6

and t

are measured with the load circuits of Figure 1 and defined as the time required for an output to cross 0.8 V or 2.4 V.

4

t

is derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 2. T he measured number is then extrapolated

back to remove the effects of charging or discharging the 50 pF capacitor. T his means that the time, t

7

, quoted in the T iming Characteristics is the true bus relinquish

time of the part and is independent of bus loading.

5

SCLK mark/space ratio (measured from a voltage level of 1.6 V) is 40/60 to 60/40.

6

SDAT A will drive higher capacitive loads, but this will add to t

12

since it increases the external RC time constant (4.7 k

//C

L

) and hence the time to reach 2.4 V.

Specifications subject to change without notice.

ABSOLUT E MAX IMUM RAT INGS*

V

DD

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

V

SS

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . +0.3 V to –7 V

AGND to DGND . . . . . . . . . . . . . . . . –0.3 V to V

DD

+ 0.3 V

V

IN

to AGND . . . . . . . . . . . . . . . . V

SS

–0.3 V to V

DD

+ 0.3 V

REF OUT , C

REF

to AGND . . . . . . . . . . . . . . . . . . 0 V to V

DD

Digital Inputs to DGND . . . . . . . . . . . –0.3 V to V

DD

+ 0.3 V

Digital Outputs to DGND . . . . . . . . . . –0.3 V to V

DD

+ 0.3 V

Operating T emperature Range

Commercial (J, K Versions) . . . . . . . . . . . . . . 0

°

C to +70

°

C

Industrial (A, B Versions) . . . . . . . . . . . . . –40

°

C to +85

°

C

Extended (T Version) . . . . . . . . . . . . . . . –55

°

C to +125

°

C

Storage T emperature Range . . . . . . . . . . . . –65

°

C to +150

°

C

Lead T emperature (Soldering, 10 sec) . . . . . . . . . . . . +300

°

C

Power Dissipation (Any Package) to +75

°

C . . . . . . . . 450 mW

Derates above +75

°

C by . . . . . . . . . . . . . . . . . . . . . 6 mW/

°

C

*Stresses above those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. T his is a stress rating only; functional operation

of the device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

WARNING!

ESD SENSITIVE DEVICE

C AUT ION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD7871/AD7872 features proprietary ESD protection circuitry, permanent dam-

age may occur on devices subjected to high energy electrostatic discharges. T herefore, proper

ESD precautions are recommended to avoid performance degradation or loss of functionality.

Figure 1. Load Circuit for Access Time

Figure 2. Load Circuit for Output Float Delay

(V

DD

= +5 V

6

5%, V

SS

= –5 V

6

5%, AGND = DGND = OV. See Figures 9, 10, 11 and 12.)

相關PDF資料 |

PDF描述 |

|---|---|

| AD7872AN | LC2MOS Complete 14-Bit, Sampling ADCs |

| AD7872BR | LC2MOS Complete 14-Bit, Sampling ADCs |

| AD7872JN | LC2MOS Complete 14-Bit, Sampling ADCs |

| AD7872JR | LC2MOS Complete 14-Bit, Sampling ADCs |

| AD7872KN | LC2MOS Complete 14-Bit, Sampling ADCs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7872AN | 功能描述:IC ADC 14BIT SAMPLING 16-DIP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7872ANZ | 功能描述:IC ADC 14BIT SAMPLING 16DIP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7872AQ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog-to-Digital Converter, 14-Bit |

| AD7872BQ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog-to-Digital Converter, 14-Bit |

| AD7872BR | 功能描述:IC ADC 14BIT SAMPLING 16-SOIC RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

發布緊急采購,3分鐘左右您將得到回復。