- 您現在的位置:買賣IC網 > PDF目錄373921 > AD7876CR (ANALOG DEVICES INC) 16-Bit, Pseudo Bipolar, Fully Diff Input, 250kSPS Serial Out, 2.7V to 5.5V Micro Power Sampling ADC 8-MSOP -40 to 85 PDF資料下載

參數資料

| 型號: | AD7876CR |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 16-Bit, Pseudo Bipolar, Fully Diff Input, 250kSPS Serial Out, 2.7V to 5.5V Micro Power Sampling ADC 8-MSOP -40 to 85 |

| 中文描述: | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, PDSO24 |

| 封裝: | MS-013AD, SOIC-24 |

| 文件頁數: | 7/20頁 |

| 文件大小: | 331K |

| 代理商: | AD7876CR |

REV. B

2

AD7870/AD7875/AD7876

–7–

to the conversion time plus the track/hold amplifier

acquisition time. For a 2.5 MHz input clock the throughput

rate is 10

μ

s max.

T he operation of the track/hold is essentially transparent to the

user. T he track/hold amplifier goes from its tracking mode to its

hold mode at the start of conversion. If the

CONVST

input is

used to start conversion then the track to hold transition occurs

on the rising edge of

CONVST

. If

CS

starts conversion, this

transition occurs on the falling edge of

CS

.

ANALOG INPUT

T he three parts differ from each other in the analog input volt-

age range that they can handle. T he AD7870 accepts

±

3 V

input signals, the AD7876 accepts a

±

10 V input range, while

the input range for the AD7875 is 0 V to +5 V.

Figure 5a shows the AD7870 analog input. T he analog input

range is

±

3 V into an input resistance of typically 15 k

. T he

designed code transitions occur midway between successive

integer LSB values (i.e., 1/2 LSB, 3/2 LSBs, 5/2 LSBs . . .

FS–3/2 LSBs). T he output code is twos complement binary

with 1 LSB = FS/4096 = 6 V/4096 = 1.46 mV. T he ideal input/

output transfer function is shown in Figure 6.

Figure 5a. AD7870 Analog Input

T he AD7876 analog input structure is shown in Figure 5b. T he

analog input range is

±

10 V into an input resistance of typically

33 k

. As before, the designed code transitions occur midway

between successive integer LSB values. T he output code is 2s

complement with 1 LSB = FS/4096 = 20 V/4096 = 4.88 mV.

T he ideal input/output transfer function is shown in Figure 6.

Figure 5b. AD7876 Analog Input

Figure 5c shows the analog input for the AD7875. T he input

range is 0 V to +5 V into an input resistance of typically 25 k

.

Once again, the designed code transitions occur midway

between successive integer LSB values. T he output code is

CONVE RT E R DE T AILS

T he AD7870/AD7875/AD7876 is a complete 12-bit A/D con-

verter, requiring no external components apart from power

supply decoupling capacitors. It is comprised of a 12-bit suc-

cessive approximation ADC based on a fast settling voltage

output DAC, a high speed comparator and SAR, a track/hold

amplifier, a 3 V buried Zener reference, a clock oscillator and

control logic.

INT E RNAL RE FE RE NCE

T he AD7870/AD7875/AD7876 has an on-chip temperature

compensated buried Zener reference that is factory trimmed to

3 V

±

10 mV. Internally it provides both the DAC reference

and the dc bias required for bipolar operation (AD7870 and

AD7876). T he reference output is available (REF OUT ) and

capable of providing up to 500

μ

A to an external load.

T he maximum recommended capacitance on REF OUT for

normal operation is 50 pF. If the reference is required for use

external to the ADC, it should be decoupled with a 200

resistor in series with a parallel combination of a 10

μ

F tanta-

lum capacitor and a 0.1

μ

F ceramic capacitor. T hese decoupling

components are required to remove voltage spikes caused by

the ADC’s internal operation.

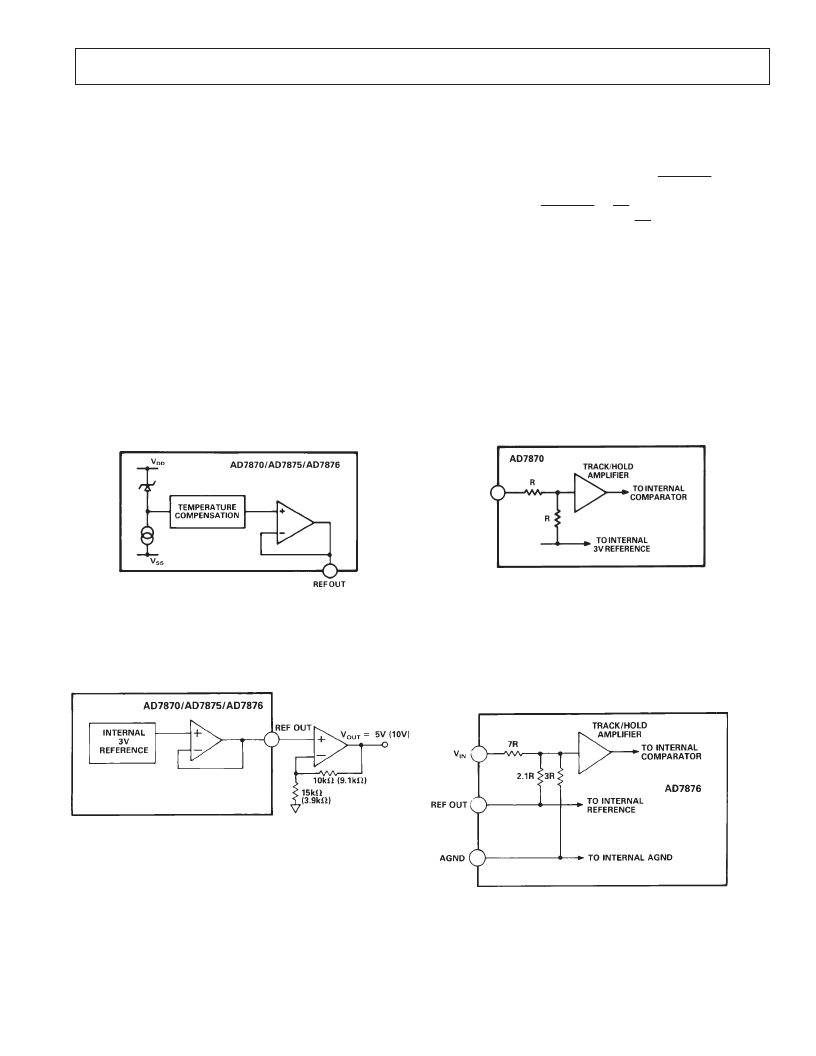

Figure 3. Reference Circuit

T he reference output voltage is 3 V. For applications using the

AD7875 or AD7876, a 5 V or 10 V reference may be required.

Figure 4 shows how to scale the 3 V REF OUT voltage to pro-

vide either a 5 V or 10 V external reference.

Figure 4. Generating a 5 V or 10 V Reference

T RACK -AND-HOLD AMPLIFIE R

T he track-and-hold amplifier on the analog input of the AD7870/

AD7875/AD7876 allows the ADC to accurately convert input

frequencies to 12-bit accuracy. T he input bandwidth of the

track/hold amplifier is much greater than the Nyquist rate of the

ADC even when the ADC is operated at its maximum through-

put rate. T he 0.1 dB cutoff frequency occurs typically at 500

kHz. T he track/hold amplifier acquires an input signal to 12-bit

accuracy in less than 2

μ

s. T he overall throughput rate is equal

相關PDF資料 |

PDF描述 |

|---|---|

| AD7876TQ | 16-Bit, Pseudo Bipolar, Fully Diff Input, 250kSPS Serial Out, 2.7V to 5.5V Micro Power Sampling ADC 8-MSOP -40 to 85 |

| AD7870AQ | LC2MOS Complete, 12-Bit, 100 kHz, Sampling ADCs |

| AD7870BQ | LC2MOS Complete, 12-Bit, 100 kHz, Sampling ADCs |

| AD7875BQ | LC2MOS Complete, 12-Bit, 100 kHz, Sampling ADCs |

| AD7875CQ | LC2MOS Complete, 12-Bit, 100 kHz, Sampling ADCs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7876CR-REEL | 功能描述:IC ADC 12BIT SAMPLING 10V 24SOIC RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7876CRZ | 功能描述:IC ADC 12BIT SAMPLING 10V 24SOIC RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7876CRZ1 | 制造商:AD 制造商全稱:Analog Devices 功能描述:LC2MOS Complete, 12-Bit, 100 kHz, Sampling ADCs |

| AD7876TQ | 制造商:Analog Devices 功能描述:ADC Single SAR 100ksps 12-bit Parallel/Serial 24-Pin CDIP 制造商:Analog Devices 功能描述:ADC SGL SAR 100KSPS 12-BIT PARALLEL/SERL 24CDIP - Rail/Tube 制造商:Rochester Electronics LLC 功能描述:12-BIT SAMPLING ADC IC - Bulk 制造商:Analog Devices 功能描述:IC ADC 12BIT SAMPLING 10V 24CDIP 制造商:Analog Devices Inc. 功能描述:Analog to Digital Converters - ADC 12-BIT SAMPLING ADC IC 制造商:Analog Devices 功能描述:CONVERTER - ADC |

| AD7876TQ/883B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog-to-Digital Converter, 12-Bit |

發布緊急采購,3分鐘左右您將得到回復。