- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373931 > AD8037AR-REEL7 (ANALOG DEVICES INC) Low Distortion, Wide Bandwidth Voltage Feedback Clamp Amps PDF資料下載

參數(shù)資料

| 型號: | AD8037AR-REEL7 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 運動控制電子 |

| 英文描述: | Low Distortion, Wide Bandwidth Voltage Feedback Clamp Amps |

| 中文描述: | OP-AMP, 10000 uV OFFSET-MAX, PDSO8 |

| 封裝: | SOIC-8 |

| 文件頁數(shù): | 18/23頁 |

| 文件大小: | 387K |

| 代理商: | AD8037AR-REEL7 |

REV. A

–18–

AD8036/AD8037

Clamping with an Offset

Some op amp circuits are required to operate with an offset

voltage. These are generally configured in the inverting mode

where the offset voltage can be summed in as one of the inputs.

Since AD8036/AD8037 clamping does not function in the in-

verting mode, it is not possible to clamp with this configuration.

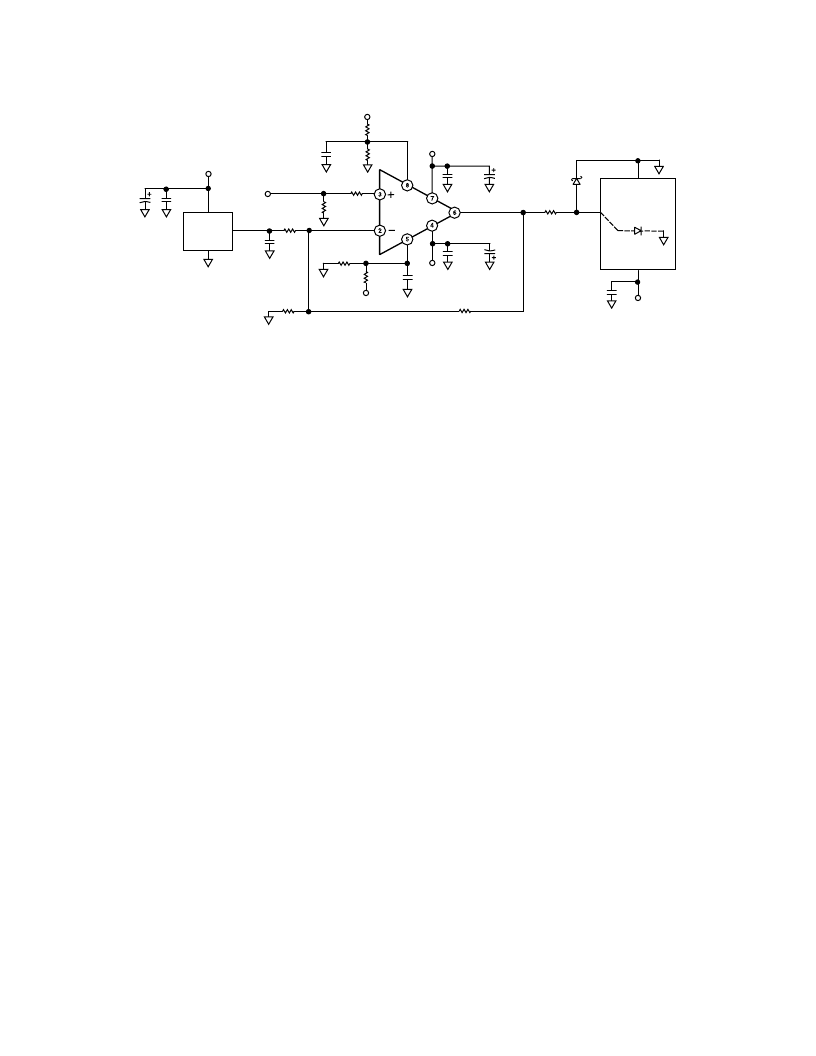

Figure 76 shows a noninverting configuration of an AD8037

that provides clamping and also has an offset.The circuit shows

the AD8037 as a driver for an AD9002, an 8-bit, 125 Msps

A/D converter and illustrates some of the considerations for us-

ing an AD8037 with offset and clamping.

The analog input range of the AD9002 is from ground to –2 V.

The input should not go more than 0.5 V outside this range in

order to prevent disruptions to the internal workings of the A/D

and to avoid drawing excess current. These requirements make

the AD8037 a prime candidate for signal conditioning.

When an offset is added to a noninverting op amp circuit, it is

fed in through a resistor to the inverting input. The result is that

the op amp must now operate at a closed-loop gain greater than

unity. For this circuit a gain of two was chosen which allows the

use of the AD8037. The feedback resistor, R2, is set at 301

for optimum performance of the AD8037 at a gain of two.

There is an interaction between the offset and the gain, so some

calculations must be performed to arrive at the proper values for

R1 and R3. For a gain of two the parallel combination of resis-

tors R1 and R3 must be equal to the feedback resistor R2. Thus

R

1

×

R

3/

R

1 +

R

3 =

R

2 = 301

The reference used to provide the offset is the AD780 whose

output is 2.5 V. This must be divided down to provide the 1 V

offset desired. Thus

2.5

V

×

R

1/(

R

1 +

R

3) = 1 V

When the two equations are solved simultaneously we get R1 =

499

and R3 = 750

(using closest 1% resistor values in all

cases). This positive 1 V offset at the input translates to a –1 V

offset at the output.

The usable input signal swing of the AD9002 is 2 V p-p. This is

centered about the –1 V offset making the usable signal range

from 0 V to –2 V. It is desirable to clamp the input signal so

that it goes no more than 100 mV outside of this range in either

direction. Thus, the high clamping level should be set at +0.1 V

and the low clamping level should be set at –2.1 V as seen at the

input of the AD9002 (output of AD8037).

Because the clamping is done at the input stage of the AD8037,

the clamping level as seen at the output is affected by not only

the gain of the circuit as previously described, but also by the

offset. Thus, in order to obtain the desired clamp levels, V

H

must be biased at +0.55 V while V

L

must be biased at –0.55 V.

The clamping levels as seen at the output can be calculated by

the following:

V

CH

=

V

OFF

+

G

×

V

H

V

CL

=

V

OFF

+

G

×

V

L

Where V

OFF

is the offset voltage that appears at the output.

The resistors used to generate the voltages for V

H

and V

L

should

be kept to a minimum in order to reduce errors due to clamp

bias current. This current is dependent on V

H

and V

L

(see Fig-

ure 61) and will create a voltage drop across whatever resistance

is in series with each clamp input. This extra error voltage is

multiplied by the closed-loop gain of the amplifier and can be

substantial, especially in high closed-loop gain configurations. A

0.1

μ

F bypass capacitor should be placed between input clamp

pins V

H

and V

L

and ground to ensure stable operation.

The 1N5712 Schottky diode is used for protection from forward

biasing the substrate diode in the AD9002 during power-up

transients.

Programmable Pulse Generator

The AD8036/AD8037’s clamp output can be set accurately and

has a well controlled flat level. This along with wide bandwidth

and high slew rate make them very well suited for programmable

level pulse generators.

Figure 77 is a schematic for a pulse generator that can directly

accept TTL generated timing signals for its input and generate

pulses at the output up to 24 V p-p with 2500 V/

μ

s slew rate.

The output levels can be programmed to anywhere in the range

–12 V to +12 V.

100

V

–0.5V to +0.5V

–2V to 0V

CLAMPING

RANGE

–2.1V to +0.1V

2.5V

+5V

10μF

–5.2V

1N5712

+5V

R2

301

V

–5V

100

V

V

H

V

L

V

IN

0.1

m

F

10

m

F

0.1

m

F

AD8037

0.1

m

F

10

m

F

R1

499

V

49.9

V

806

V

+5V

0.1

m

F

806

V

–5V

100

V

R3

750

V

0.1

m

F

0.1

m

F

AD780

49.9

V

AD9002

V

IN

= –2V TO 0V

SUBSTRATE

DIODE

0.1

m

F

Figure 76. Gain of Two, Noninverting with Offset AD8037 Driving an AD9002—8-Bit, 125 MSPS A/D Converter

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD8036-EB | Low Distortion, Wide Bandwidth Voltage Feedback Clamp Amps |

| AD8037ACHIPS | Connector assemblies, Test RoHS Compliant: Yes |

| AD8037AN | Low Distortion, Wide Bandwidth Voltage Feedback Clamp Amps |

| AD8037AR | Low Distortion, Wide Bandwidth Voltage Feedback Clamp Amps |

| AD8036ACHIPS | Low Distortion, Wide Bandwidth Voltage Feedback Clamp Amps |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD8037ARZ | 功能描述:IC OPAMP VF ULDIST LN 70MA 8SOIC RoHS:是 類別:集成電路 (IC) >> Linear - Amplifiers - Instrumentation 系列:CLAMPIN™ 標(biāo)準(zhǔn)包裝:2,500 系列:- 放大器類型:通用 電路數(shù):4 輸出類型:- 轉(zhuǎn)換速率:0.6 V/µs 增益帶寬積:1MHz -3db帶寬:- 電流 - 輸入偏壓:45nA 電壓 - 輸入偏移:2000µV 電流 - 電源:1.4mA 電流 - 輸出 / 通道:40mA 電壓 - 電源,單路/雙路(±):3 V ~ 32 V,±1.5 V ~ 16 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:14-TSSOP(0.173",4.40mm 寬) 供應(yīng)商設(shè)備封裝:14-TSSOP 包裝:帶卷 (TR) 其它名稱:LM324ADTBR2G-NDLM324ADTBR2GOSTR |

| AD8037ARZ-REEL | 功能描述:IC OPAMP VF ULDIST LN 70MA 8SOIC RoHS:是 類別:集成電路 (IC) >> Linear - Amplifiers - Instrumentation 系列:CLAMPIN™ 標(biāo)準(zhǔn)包裝:50 系列:- 放大器類型:J-FET 電路數(shù):2 輸出類型:- 轉(zhuǎn)換速率:3.5 V/µs 增益帶寬積:1MHz -3db帶寬:- 電流 - 輸入偏壓:30pA 電壓 - 輸入偏移:2000µV 電流 - 電源:200µA 電流 - 輸出 / 通道:- 電壓 - 電源,單路/雙路(±):7 V ~ 36 V,±3.5 V ~ 18 V 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:8-DIP(0.300",7.62mm) 供應(yīng)商設(shè)備封裝:8-PDIP 包裝:管件 |

| AD8037ARZ-REEL7 | 功能描述:IC OPAMP VF ULDIST LN 70MA 8SOIC RoHS:是 類別:集成電路 (IC) >> Linear - Amplifiers - Instrumentation 系列:CLAMPIN™ 標(biāo)準(zhǔn)包裝:150 系列:- 放大器類型:音頻 電路數(shù):2 輸出類型:- 轉(zhuǎn)換速率:5 V/µs 增益帶寬積:12MHz -3db帶寬:- 電流 - 輸入偏壓:100nA 電壓 - 輸入偏移:500µV 電流 - 電源:6mA 電流 - 輸出 / 通道:50mA 電壓 - 電源,單路/雙路(±):4 V ~ 32 V,±2 V ~ 16 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:8-TSSOP(0.173",4.40mm 寬) 供應(yīng)商設(shè)備封裝:8-TSSOP 包裝:管件 |

| AD8037-EB | 功能描述:BOARD EVAL FOR AD8037 RoHS:否 類別:編程器,開發(fā)系統(tǒng) >> 評估板 - 運算放大器 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- |

| AD8037SRZ-EP | 功能描述:IC OPAMP VF LP LN LDIST 8SOIC 制造商:analog devices inc. 系列:- 包裝:管件 零件狀態(tài):在售 放大器類型:電壓反饋 電路數(shù):1 輸出類型:- 壓擺率:1500 V/μs -3db 帶寬:270MHz 電流 - 輸入偏置:3μA 電壓 - 輸入失調(diào):2mV 電流 - 電源:18.5mA 電流 - 輸出/通道:70mA 電壓 - 電源,單/雙(±):±3 V ~ 6 V 工作溫度:-55°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:8-SOIC(0.154",3.90mm 寬) 供應(yīng)商器件封裝:8-SOIC 標(biāo)準(zhǔn)包裝:1 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。