參數資料

| 型號: | AD8304ARUZ |

| 廠商: | Analog Devices Inc |

| 文件頁數: | 1/20頁 |

| 文件大小: | 0K |

| 描述: | IC LOGARITHM CONV 160DB 14-TSSOP |

| 設計資源: | Interfacing ADL5315 to Translinear Logarithmic Amplifier (CN0056) Interfacing ADL5317 High Side Current Mirror to a Translinear Logarithmic Amplifier in an Avalanche Photodiode Power Detector |

| 標準包裝: | 1 |

| 類型: | 對數轉換器 |

| 應用: | 光纖 |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 14-TSSOP(0.173",4.40mm 寬) |

| 供應商設備封裝: | 14-TSSOP |

| 包裝: | 管件 |

| 產品目錄頁面: | 550 (CN2011-ZH PDF) |

REV. A

a

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

Fax: 781/326-8703

Analog Devices, Inc., 2002

AD8304

160 dB Range (100 pA –10 mA)

Logarithmic Converter

FEATURES

Optimized for Fiber Optic Photodiode Interfacing

Eight Full Decades of Range

Law Conformance 0.1 dB from 1 nA to 1 mA

Single-Supply Operation (3.0 V– 5.5 V)

Complete and Temperature Stable

Accurate Laser-Trimmed Scaling:

Logarithmic Slope of 10 mV/dB (at VLOG Pin)

Basic Logarithmic Intercept at 100 pA

Easy Adjustment of Slope and Intercept

Output Bandwidth of 10 MHz, 15 V/ s Slew Rate

1-, 2-, or 3-Pole Low-Pass Filtering at Output

Miniature 14-Lead Package (TSSOP)

Low Power: ~4.5 mA Quiescent Current (Enabled)

APPLICATIONS

High Accuracy Optical Power Measurement

Wide Range Baseband Log Compression

Versatile Detector for APC Loops

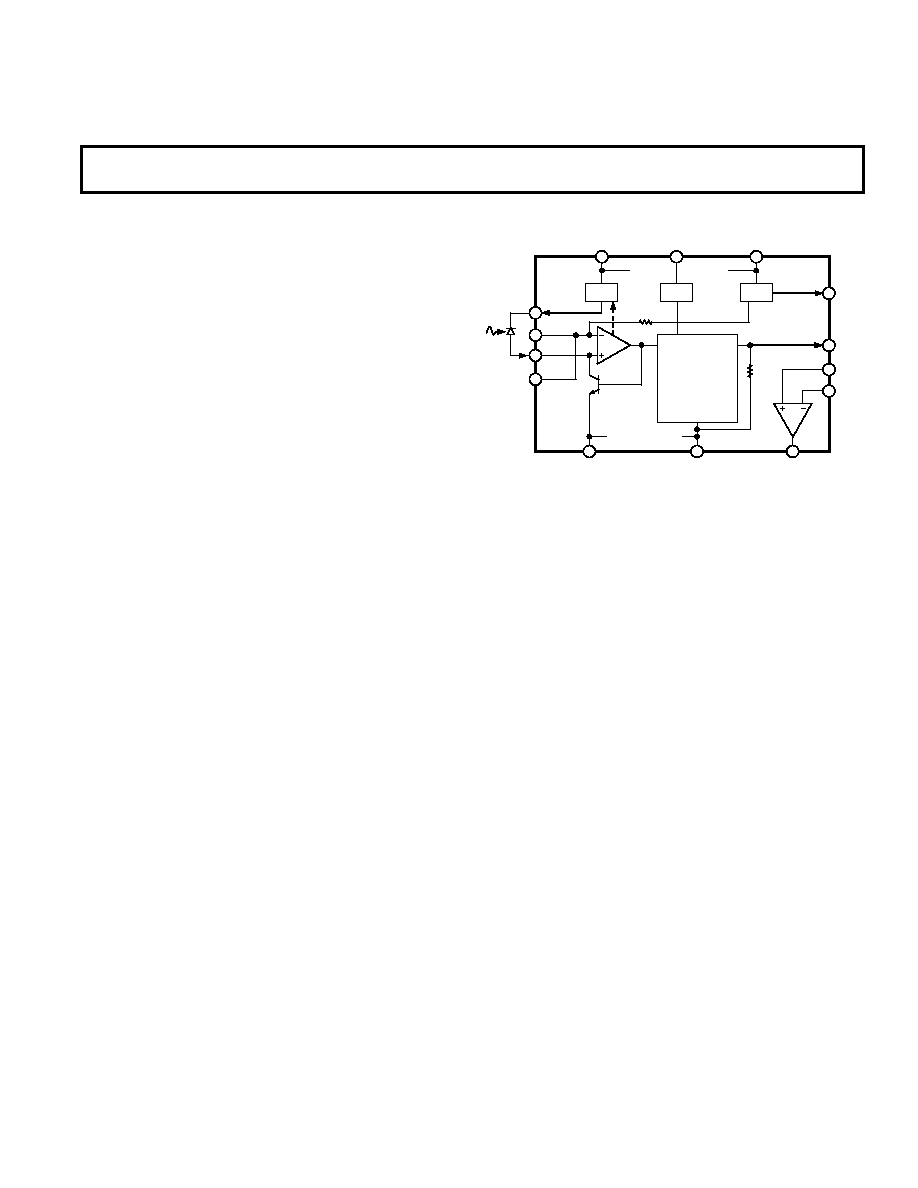

FUNCTIONAL BLOCK DIAGRAM

6

3

4

PDB

BIAS

VREF

10

2

12

IPD

VPDB

VSUM

INPT

VSUM 5

1

VNEG

~10k

ACOM

14

VPS2

PWDN

VPS1

VREF

7

VLOG

8

BFIN

9

BFNG

13

TEMPERATURE

COMPENSATION

5k

11

VOUT

0.5V

AD8304

PRODUCT DESCRIPTION

The AD8304 is a monolithic logarithmic detector optimized for

the measurement of low frequency signal power in fiber optic

systems. It uses an advanced translinear technique to provide an

exceptionally large dynamic range in a versatile and easily used

form. Its wide measurement range and accuracy are achieved

using proprietary design techniques and precise laser trimming.

In most applications only a single positive supply, VP, of 5 V

will be required, but 3.0 V to 5.5 V can be used, and certain

applications benefit from the added use of a negative supply,

VN. When using low supply voltages, the log slope is readily

altered to fit the available span. The low quiescent current and

chip disable features facilitate use in battery-operated applications.

The input current, IPD, flows in the collector of an optimally

scaled NPN transistor, connected in a feedback path around a

low offset JFET amplifier. The current-summing input node

operates at a constant voltage, independent of current, with a

default value of 0.5 V; this may be adjusted over a wide range,

including ground or below, using an optional negative supply.

An adaptive biasing scheme is provided for reducing the dark

current at very low light input levels. The voltage at Pin VPDB

applies approximately 0.1 V across the diode for IPD = 100 pA,

rising linearly with current to 2.0 V of net bias at IPD = 10 mA.

The input pin INPT is flanked by the guard pins VSUM that

track the voltage at the summing node to minimize leakage.

The default value of the logarithmic slope at the output VLOG is

accurately scaled to 10 mV/dB (200 mV/decade). The resistance

at this output is laser-trimmed to 5 k

, allowing the slope to be

lowered by shunting it with an external resistance; the addition

of a capacitor at this pin provides a simple low-pass filter. The

intermediate voltage VLOG is buffered in an output stage that can

swing to within about 100 mV of ground (or VN) and the posi-

tive supply, VP, and provides a peak current drive capacity of

±20 mA. The slope can be increased using the buffer and a pair

of external feedback resistors. An accurate voltage reference of

2V is also provided to facilitate the repositioning of the intercept.

Many operational modes are possible. For example, low-pass filters

of up to three poles may be implemented, to reduce the output

noise at low input currents. The buffer may also serve as a com-

parator, with or without hysteresis, using the 2 V reference, for

example, in alarm applications. The incremental bandwidth of

a translinear logarithmic amplifier inherently diminishes for small

input currents. At the 1 nA level, the AD8304’s bandwidth is

about 2 kHz, but this increases in proportion to IPD up to a

maximum value of 10 MHz.

The AD8304 is available in a 14-lead TSSOP package and specified

for operation from –40

°C to +85°C.

相關PDF資料 |

PDF描述 |

|---|---|

| VE-27P-MW-B1 | CONVERTER MOD DC/DC 13.8V 100W |

| MAX4375HEUB+ | IC AMP CURRENT SENSE 10-UMAX |

| VI-J3P-MW-S | CONVERTER MOD DC/DC 13.8V 100W |

| MAX4375TEUB+ | IC AMP CURRENT SENSE 10-UMAX |

| VE-25T-MW-B1 | CONVERTER MOD DC/DC 6.5V 100W |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD8304ARUZ | 制造商:Analog Devices 功能描述:Logarithmic Amplifier IC |

| AD8304ARUZ-RL7 | 功能描述:IC LOGARITHM CONV 160DB 14-TSSOP RoHS:是 類別:集成電路 (IC) >> 線性 - 放大器 - 專用 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:60 系列:- 類型:可變增益放大器 應用:CATV 安裝類型:表面貼裝 封裝/外殼:20-WQFN 裸露焊盤 供應商設備封裝:20-TQFN-EP(5x5) 包裝:托盤 |

| AD8304-EVAL | 制造商:Analog Devices 功能描述:LTSSOP 160DB-RANGE LOGARITHMIC CONVERTER - Bulk |

| AD8304-EVALZ | 制造商:Analog Devices 功能描述:Evaluation Kit For 160 DB Range Logarithmic Converter 制造商:Analog Devices 功能描述:EVAL KIT FOR 160 DB RANGE (100 PA -10 MA) LOGARITHMIC CNVRTR - Bulk 制造商:Analog Devices 功能描述:EVAL LOGARITHMIC DECTECTOR AD8304 |

| AD8304XRU | 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。