- 您現在的位置:買賣IC網 > PDF目錄373942 > AD8306-EVAL (Analog Devices, Inc.) 5 MHz-400 MHz 100 dB High Precision Limiting-Logarithmic Amplifier PDF資料下載

參數資料

| 型號: | AD8306-EVAL |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 運動控制電子 |

| 英文描述: | 5 MHz-400 MHz 100 dB High Precision Limiting-Logarithmic Amplifier |

| 中文描述: | 5兆赫,400兆赫100分貝高精度極限,對數放大器 |

| 文件頁數: | 2/16頁 |

| 文件大小: | 397K |

| 代理商: | AD8306-EVAL |

REV. A

–2–

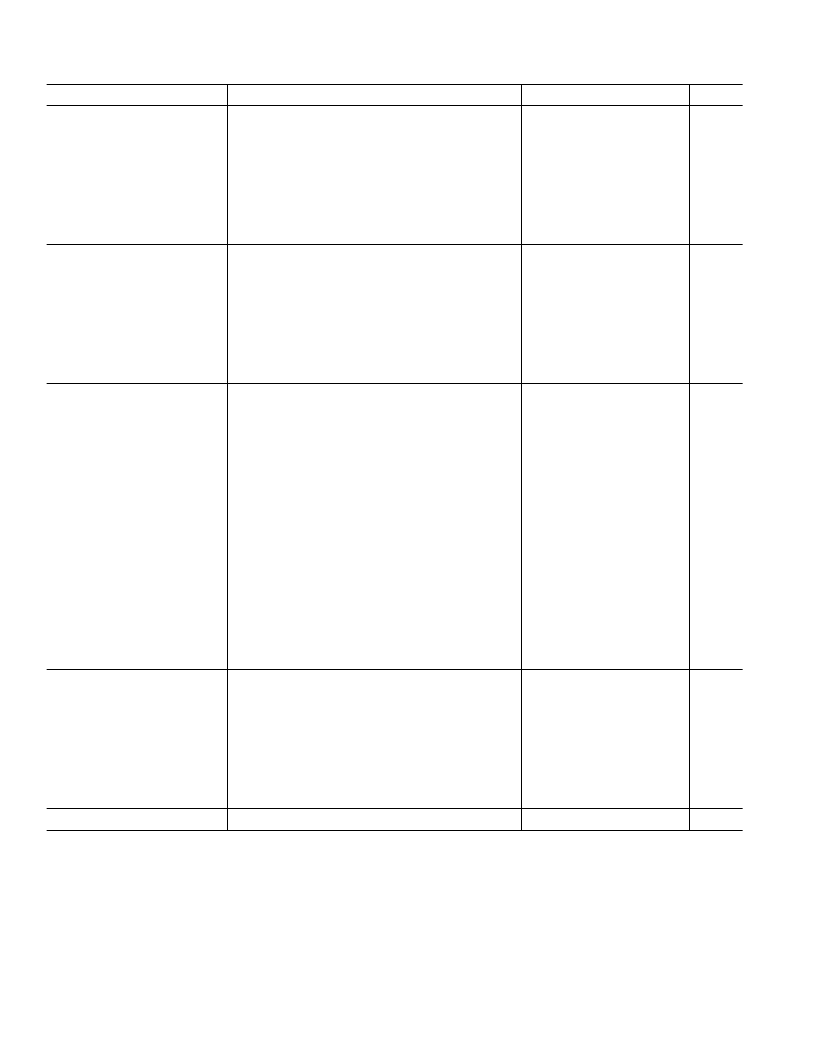

AD8306–SPECIFICATIONS

Parameter

Conditions

Min

1

Typ

Max

1

Units

INPUT STAGE

Maximum Input

2

(Inputs INHI, INLO)

Differential Drive, p-p

±

3.5

±

4

+9

+22

1.28

–78

1000

2.5

1.725

V

dBV

dBm

nV/

√

Hz

dBm

pF

V

Equivalent Power in 50

Noise Floor

Equivalent Power in 50

Input Resistance

Input Capacitance

DC Bias Voltage

Terminated in 52.3

i

R

IN

Terminated 50

Source

400 MHz Bandwidth

From INHI to INLO

From INHI to INLO

Either Input

800

1200

LIMITING AMPLIFIER

Usable Frequency Range

At Limiter Output

Phase Variation at 100 MHz

Limiter Output Current

Versus Temperature

Input Range

3

Maximum Output Voltage

Rise/Fall Time (10%–90%)

(Outputs LMHI, LMLO)

5

400

MHz

MHz

Degrees

mA

%/

°

C

dBV

V

ns

R

LOAD

= R

LIM

= 50

, to –10 dB Point

Over Input Range –73 dBV to –3 dBV

Nominally 400 mV/R

LIM

–40

°

C

≤

T

A

≤

+85

°

C

585

±

2

1

–0.008

0

10

–78

1

+9

At Either LMHI or LMLO, wrt VPS2

R

LOAD

= 50

, 40

≤

R

LIM

≤

400

1.25

0.6

LOGARITHMIC AMPLIFIER

±

3 dB Error Dynamic Range

Transfer Slope

4

(Output VLOG)

From Noise Floor to Maximum Input

f = 10 MHz

f = 100 MHz

–40

°

C < T

A

< +85

°

C

f = 10 MHz

f = 100 MHz

–40

°

C

≤

T

A

≤

+85

°

C

100

20

19.6

20

–108

–108.4

–108

–0.009

±

0.4

0.34

2.34

2.10

50

1.0

0.3

3.5

120

73

dB

mV/dB

mV/dB

mV/dB

dBV

dBV

dBV

dB/

°

C

dB

V

V

V

mA

MHz

ns

ns

19.5

20.5

Over Temperature

Intercept (Log Offset)

4

19.3

–109.5

20.7

–106.5

Over Temperature

Temperature Sensitivity

Linearity Error (Ripple)

Output Voltage

–111

–105

Input from –80 dBV to +0 dBV

Input = –91 dBV, V

S

= +5 V, +2.7 V

Input = +9 dBV, V

S

= +5 V

Input = –3 dBV, V

S

= +3 V

2.75

Minimum Load Resistance, R

L

Maximum Sink Current

Output Resistance

Small-Signal Bandwidth

Output Settling Time to 2%

Rise/Fall Time (10%–90%)

40

0.75

To Ground

1.25

Large Scale Input, +3 dBV, R

L

≥

50

, C

L

≤

100 pF

Large Scale Input, +3 dBV, R

L

≥

50

, C

L

≤

100 pF

220

100

POWER INTERFACES

Supply Voltage, V

S

Quiescent Current

Over Temperature

Disable Current

Additional Bias for Limiter

Logic Level to Enable Power

Input Current when HI

Logic Level to Disable Power

2.7

13

11

5

16

16

0.01

2.0

6.5

20

23

4

2.25

V

S

60

V

mA

mA

μ

A

mA

V

μ

A

V

Zero-Signal, LMDR Open

–40

°

C < T

A

< +85

°

C

–40

°

C < T

A

< +85

°

C

R

LIM

= 400

(See Text)

HI Condition, –40

°

C < T

A

< +85

°

C

3 V at ENBL, –40

°

C < T

A

< +85

°

C

LO Condition, –40

°

C < T

A

< +85

°

C

2.7

40

1

–0.5

TRANSISTOR COUNT

# of Transistors

207

207

NOTES

1

Minimum and maximum specified limits on parameters that are guaranteed but not tested are six sigma values.

2

The input level is specified in “dBV” since logarithmic amplifiers respond strictly to voltage, not power. 0 dBV corresponds to a sinusoidal single-frequency input of

1 V rms. A power level of 0 dBm (1 mW) in a 50

termination corresponds to an input of 0.2236 V rms. Hence, in the special case of 50

termination, dBV values

can be converted into dBm by adding a fixed offset of +13 to the dBV rms value.

3

Due to the extremely high Gain Bandwidth Product of the AD8306, the output of either LMHI or LMLO will be unstable for levels below –78 dBV (–65 dBm, re 50

).

4

Standard deviation remains essentially constant over frequency. See Figures 13, 14, 16 and 17.

Specifications subject to change without notice.

(V

S

= +5 V, T

A

= +25

8

C, f = 10 MHz, unless otherwise noted)

相關PDF資料 |

PDF描述 |

|---|---|

| AD8306ACHIPS | 5 MHz-400 MHz 100 dB High Precision Limiting-Logarithmic Amplifier |

| AD8306AR | 5 MHz-400 MHz 100 dB High Precision Limiting-Logarithmic Amplifier |

| AD8306AR-REEL | 5 MHz-400 MHz 100 dB High Precision Limiting-Logarithmic Amplifier |

| AD8306AR-REEL7 | 5 MHz-400 MHz 100 dB High Precision Limiting-Logarithmic Amplifier |

| AD8307AN | Low Cost DC-500 MHz, 92 dB Logarithmic Amplifier |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD8306-EVALZ | 制造商:Analog Devices 功能描述:Evaluation Board For AD8306 制造商:Analog Devices 功能描述:EVALUATION BOARDS - Bulk 制造商:Analog Devices 功能描述:IC LOGARITHMIC AMPLIFIER ((NS)) |

| AD8307 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Low Cost DC-500 MHz, 92 dB Logarithmic Amplifier |

| AD8307_06 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Low Cost DC-500 MHz, 92 dB Logarithmic Amplifier |

| AD8307AN | 功能描述:IC LOGARITHMIC AMP 8-DIP RoHS:否 類別:集成電路 (IC) >> 線性 - 放大器 - 專用 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:60 系列:- 類型:可變增益放大器 應用:CATV 安裝類型:表面貼裝 封裝/外殼:20-WQFN 裸露焊盤 供應商設備封裝:20-TQFN-EP(5x5) 包裝:托盤 |

| AD8307ANZ | 功能描述:IC LOGARITHMIC AMP 8-DIP RoHS:是 類別:集成電路 (IC) >> 線性 - 放大器 - 專用 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:60 系列:- 類型:可變增益放大器 應用:CATV 安裝類型:表面貼裝 封裝/外殼:20-WQFN 裸露焊盤 供應商設備封裝:20-TQFN-EP(5x5) 包裝:托盤 |

發布緊急采購,3分鐘左右您將得到回復。