- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373959 > AD9200JSTRL (ANALOG DEVICES INC) Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter PDF資料下載

參數(shù)資料

| 型號: | AD9200JSTRL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter |

| 中文描述: | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

| 封裝: | PLASTIC, LQFP-48 |

| 文件頁數(shù): | 15/24頁 |

| 文件大小: | 338K |

| 代理商: | AD9200JSTRL |

AD9200

–15–

REV. E

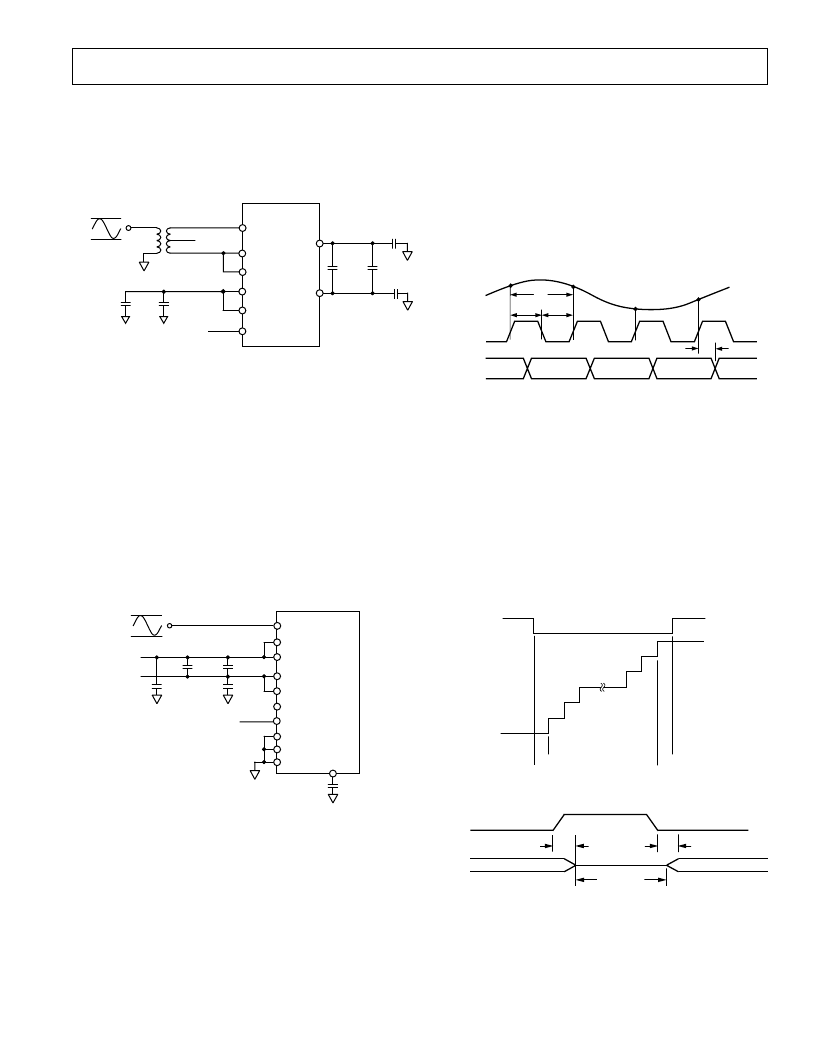

DIFFERENTIAL INPUT OPERATION

The AD9200 will accept differential input signals. This function

may be used by shorting REFTS and REFBS and driving them

as one leg of the differential signal (the top leg is driven into

AIN). In the configuration below, the AD9200 is accepting a

1 V p-p signal. See Figure 29.

AIN

REFTS

REFTF

REFBF

REFBS

AD9200

0.1

m

F

10

m

F

0.1

m

F

0.1

m

F

2V

1V

AVDD/2

VREF

REFSENSE

MODE

AVDD/2

0.1

m

F

1.0

m

F

Figure 29. Differential Input

AD876 MODE OF OPERATION

The AD9200 may be dropped into the AD876 socket. This will

allow AD876 users to take advantage of the reduced power

consumption realized when running the AD9200 on a 3.0 V

analog supply.

Figure 30 shows the pin functions of the AD876 and AD9200.

The grounded REFSENSE pin and floating MODE pin effec-

tively put the AD9200 in the external reference mode. The

external reference input for the AD876 will now be placed on

the reference pins of the AD9200.

The clamp controls will be grounded by the AD876 socket. The

AD9200 has a 3 clock cycle delay compared to a 3.5 cycle delay

of the AD876.

4V

2V

0.1

m

F

0.1

m

F

AVDD

10

m

F

0.1

m

F

4V

2V

AIN

REFTS

REFTF

REFBF

REFBS

CLAMP

CLAMPIN

OTR

REFSENSE

AD9200

MODE

NC

VREF

0.1

m

F

Figure 30. AD876 Mode

CLOCK INPUT

The AD9200 clock input is buffered internally with an inverter

powered from the AVDD pin. This feature allows the AD9200

to accommodate either +5 V or +3.3 V CMOS logic input sig-

nal swings with the input threshold for the CLK pin nominally

at AVDD/2.

The pipelined architecture of the AD9200 operates on both

rising and falling edges of the input clock. To minimize duty

cycle variations the recommended logic family to drive the clock

input is high speed or advanced CMOS (HC/HCT, AC/ACT)

logic. CMOS logic provides both symmetrical voltage threshold

levels and sufficient rise and fall times to support 20 MSPS

operation. The AD9200 is designed to support a conversion rate

of 20 MSPS; running the part at slightly faster clock rates may

be possible, although at reduced performance levels. Conversely,

some slight performance improvements might be realized by

clocking the AD9200 at slower clock rates.

t

CL

t

CH

t

C

25ns

DATA 1

DATA

OUTPUT

INPUT

CLOCK

ANALOG

INPUT

S1

S2

S3

S4

Figure 31. Timing Diagram

The power dissipated by the output buffers is largely propor-

tional to the clock frequency; running at reduced clock rates

provides a reduction in power consumption.

DIGITAL INPUTS AND OUTPUTS

Each of the AD9200 digital control inputs, THREE-STATE

and STBY are reference to analog ground. The clock is also

referenced to analog ground.

The format of the digital output is straight binary (see Figure

32). A low power mode feature is provided such that for STBY

= HIGH and the clock disabled, the static power of the AD9200

will drop below 5 mW.

OTR

–FS

–FS+1LSB

+FS–1LSB

+FS

Figure 32. Output Data Format

HIGH

IMPEDANCE

t

DHZ

t

DEN

THREE-

STATE

DATA

(D0–D9)

Figure 33. Three-State Timing Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9201 | Dual Channel, 20 MHz 10-Bit Resolution CMOS ADC |

| AD9201-EVAL | Dual Channel, 20 MHz 10-Bit Resolution CMOS ADC |

| AD9201ARS | Dual Channel, 20 MHz 10-Bit Resolution CMOS ADC |

| AD9201EVALBOARD | Octal I2C 16-Bit Rail-to-Rail DACs in 16-Lead SSOP; Package: SSOP; No of Pins: 16; Temperature Range: -40°C to +85°C |

| AD9203 | 10-Bit, 40 MSPS, 3 V, 74 mW A/D Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9200JSTZ | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述: |

| AD9200KST | 制造商:Rochester Electronics LLC 功能描述:10-BIT 20 MSPS, 80 MW CMOS A/D CONVERTER - Tape and Reel 制造商:Analog Devices 功能描述: |

| AD9200KSTRL | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel 制造商:Analog Devices 功能描述: |

| AD9200KSTZ | 制造商:Analog Devices 功能描述:ADC SGL PIPELINED 20MSPS 10-BIT PARALLEL 48LQFP - Trays |

| AD9200KSTZRL | 制造商:Analog Devices 功能描述:ADC SGL PIPELINED 20MSPS 10-BIT PARALLEL 48LQFP - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。