- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373961 > AD9238BST-40 (ANALOG DEVICES INC) 12-Bit, 20/40/65 MSPS Dual A/D Converter PDF資料下載

參數(shù)資料

| 型號: | AD9238BST-40 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 12-Bit, 20/40/65 MSPS Dual A/D Converter |

| 中文描述: | 2-CH 12-BIT FLASH METHOD ADC, PARALLEL ACCESS, PQFP64 |

| 封裝: | LEAD FREE, MS-026-BBD, LQFP-64 |

| 文件頁數(shù): | 12/24頁 |

| 文件大小: | 1737K |

| 代理商: | AD9238BST-40 |

AD9238

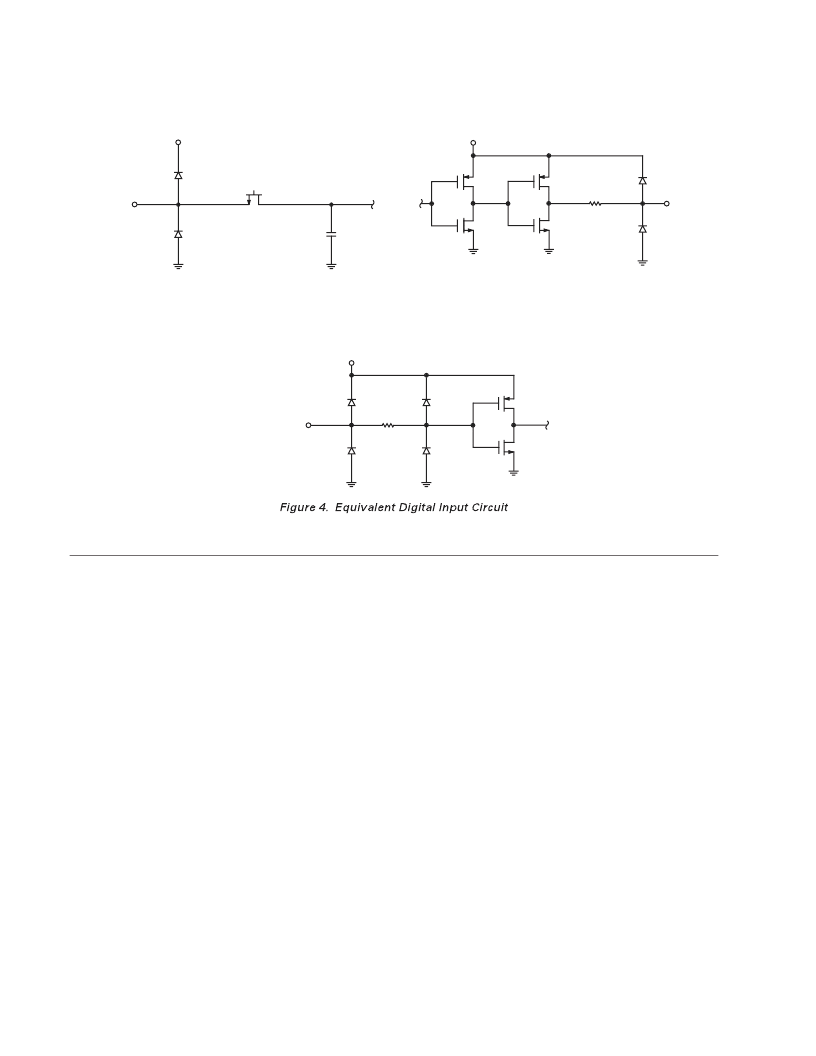

Equivalent Circuits

–12–

AVDD

VIN+_A, VIN–_A,

VIN+_B, VIN–_B,

Figure 2. Equivalent Analog Input Circuit

Figure 3. Equivalent Digital Output Circuit

AVDD

CLK_A, CLK_B

DCS, DFS,

MUX_SELECT

SHARED_REF

THEORY OF OPERATION

The AD9238 consists of two high performance analog-to-digital

converters (ADCs) that are based on the AD9235 converter core.

The dual ADC paths are independent, except for a shared internal

band gap reference source, V

REF

. Each of the ADC’s paths consists

of a proprietary front end sample-and-hold amplifier (SHA)

followed by a pipelined switched capacitor ADC. The pipelined

ADC is divided into three sections, consisting of a 4-bit first stage

followed by eight 1.5-bit stages and a final 3-bit flash. Each stage

provides sufficient overlap to correct for flash errors in the preced-

ing stages. The quantized outputs from each stage are combined

through the digital correction logic block into a final 12-bit result.

The pipelined architecture permits the first stage to operate on a

new input sample, while the remaining stages operate on preceding

samples. Sampling occurs on the rising edge of the respective clock.

Each stage of the pipeline, excluding the last, consists of a low

resolution flash ADC and a residual multiplier to drive the next

stage of the pipeline. The residual multiplier uses the flash ADC

output to control a switched capacitor digital-to-analog converter

(DAC) of the same resolution. The DAC output is subtracted from

the stage’s input signal and the residual is amplified (multiplied)

to drive the next pipeline stage. The residual multiplier stage is

also called a multiplying DAC (MDAC). One bit of redundancy

is used in each one of the stages to facilitate digital correction of

flash errors. The last stage simply consists of a flash ADC.

The input stage contains a differential SHA that can be config-

ured as ac- or dc-coupled in differential or single-ended modes.

The output-staging block aligns the data, carries out the error

correction, and passes the data to the output buffers. The output

buffers are powered from a separate supply, allowing adjustment

of the output voltage swing.

ANALOG INPUT

The analog input to the AD9238 is a differential switched capacitor,

SHA, that has been designed for optimum performance while

processing a differential input signal. The SHA input accepts inputs

over a wide common-mode range. An input common-mode voltage

of midsupply is recommended to maintain optimal performance.

The SHA input is a differential switched capacitor circuit. In

Figure 5, the clock signal alternatively switches the SHA between

sample mode and hold mode. When the SHA is switched into

sample mode, the signal source must be capable of charging the

sample capacitors and settling within one-half of a clock cycle. A

small resistor in series with each input can help reduce the peak

transient current required from the output stage of the driving

source. Also, a small shunt capacitor can be placed across the inputs

to provide dynamic charging currents. This passive network will

create a low-pass filter at the ADC’s input; therefore, the precise

values are dependant on the application. In IF undersampling

applications, any shunt capacitors should be removed. In combi-

nation with the driving source impedance, they would limit the

input bandwidth. For best dynamic performance, the source

impedances driving VIN+ and VIN– should be matched such that

common-mode settling errors are symmetrical. These errors will

be reduced by the common-mode rejection of the ADC.

REV. A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9238BST-65 | 12-Bit, 20/40/65 MSPS Dual A/D Converter |

| AD9238BSTRL-20 | 12-Bit, 20/40/65 MSPS Dual A/D Converter |

| AD9238BSTRL-40 | 12-Bit, 20/40/65 MSPS Dual A/D Converter |

| AD9238BSTRL-65 | 12-Bit, 20/40/65 MSPS Dual A/D Converter |

| AD9240 | Complete 14-Bit, 10 MSPS Monolithic A/D Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9238BST-40EBZ | 制造商:Analog Devices 功能描述:Evaluation Board For AD9238 Dual A/D Converter ,12-Bit, 20 MSPS/40 MSPS/65 MSPS 制造商:Analog Devices 功能描述:EVAL BD FOR AD9238 DUAL A/D CNVRTR ,12-BIT, 20 MSPS/40 MSPS/ - Bulk |

| AD9238BST-40PCB | 制造商:Analog Devices 功能描述:Evaluation Board For AD9238 Dual A/D Converter ,12-Bit, 20 MSPS/40 MSPS/65 MSPS 制造商:Analog Devices 功能描述:EVAL BD FOR AD9238 DUAL A/D CNVRTR ,12-BIT, 20 MSPS/40 MSPS/ - Bulk |

| AD9238BST-40PCBZ | 制造商:Analog Devices 功能描述:DUAL 12 BIT 3V CMOS 20/40/65 MSPS ADC - Bulk |

| AD9238BST-65 | 功能描述:IC ADC 12BIT DUAL 65MSPS 64-LQFP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:- 位數(shù):12 采樣率(每秒):3M 數(shù)據(jù)接口:- 轉(zhuǎn)換器數(shù)目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應(yīng)商設(shè)備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數(shù)目和類型:- |

| AD9238BST-65PCB | 制造商:Analog Devices 功能描述:Evaluation Board For AD9238 Dual A/D Converter ,12-Bit, 20 MSPS/40 MSPS/65 MSPS 制造商:Rochester Electronics LLC 功能描述:DUAL 12 BIT 3V CMOS 20/40/65 MSPS ADC - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。