- 您現在的位置:買賣IC網 > PDF目錄373962 > AD9248BST-20 (ANALOG DEVICES INC) 14-Bit, 20/40/65 MSPS Dual A/ D Converter PDF資料下載

參數資料

| 型號: | AD9248BST-20 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 14-Bit, 20/40/65 MSPS Dual A/ D Converter |

| 中文描述: | DUAL 1-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP64 |

| 封裝: | MS-026BBD, LQFP-64 |

| 文件頁數: | 1/23頁 |

| 文件大小: | 419K |

| 代理商: | AD9248BST-20 |

14-Bit, 20/40/65 MSPS

Dual A/

D Converter

Preliminary Technical Data

AD9248

FEATURES

Integrated Dual 14-Bit A-to-D Converters

Single 3 V Supply Operation (2.7 V to 3.6 V)

SNR = 73 dBc (to Nyquist, AD9248-65)

SFDR = 83 dBc (to Nyquist, AD9248-65)

Low Power: 600 mW at 65 MSPS

Differential Input with 500 MHz 3 dB Bandwidth

Exceptional Cross Talk Immunity > 85dB

Flexible Analog Input: 1 V p-p to 2 V p-p Range

Offset Binary or Twos Complement Data Format

Clock Duty Cycle Stabilizer

Rev.

PrE

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its use,

nor for any infringements of patents or other rights of third parties that may

result from its use. Specifications subject to change without notice. No license

is granted by implication or otherwise under any patent or patent rights of

Analog Devices. Trademarks and registered trademarks are the property of

their respective companies.

6/29/2004

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106,

U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703

200

4

Analog Devices, Inc. All rights reserved.

www.analog.com

APPLICATIONS

Ultrasound Equipment

IF Sampling in Communications Receivers:

IS-95, CDMA One, IMT-2000

Battery-Powered Instruments

Hand-Held Scopemeters

Low Cost Digital Oscilloscopes

GENERAL DESCRIPTION

The AD9248 is a dual, 3 V, 14-bit, 20/40/65 MSPS analog-to-

digital converter. It features dual high performance sample-and

hold amplifiers and an integrated voltage reference. The

AD9248 uses a multistage differential pipelined architecture

with output error correction logic to provide 14-bit accuracy

and guarantee no missing codes over the full operating

temperature range at up to 65 MSPS data rates. The wide

bandwidth, differential SHA allows for a variety of user

selectable input ranges and offsets including single-ended

applications. It is suitable for various applications including

multiplexed systems that switch full-scale voltage levels in

successive channels and for sampling inputs at frequencies well

beyond the Nyquist rate.

Dual single-ended clock inputs are used to control all internal

conversion cycles. A duty cycle stabilizer is available on the

AD9248-65 and can compensate for wide variations in the

clock duty cycle, allowing the converters to maintain excellent

performance. The digital output data is presented in either

straight binary or twos complement format. Out-of-range

signals indicate an overflow condition, which can be used with

the most significant bit to determine low or high overflow.

Fabricated on an advanced CMOS process, the AD9248 is

available in a space saving 64-lead LQFP and is specified over

the industrial temperature range (–40 C to +85 C).

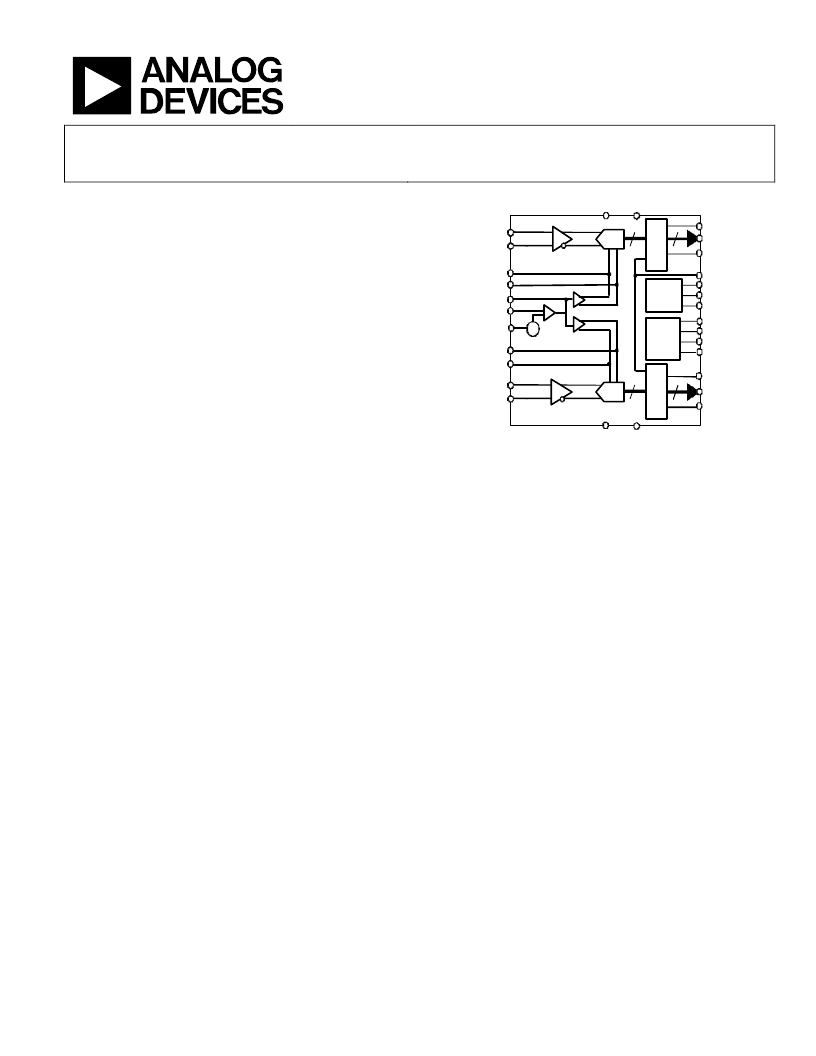

ADC

D13

A

-D

0A

OEB_A

O

B

AGND

VIN- _A

CLK_A

CLK_B

AD9248

SHA

14

VIN+_A

DCS

SHARED_REF

PWDN_A

PWDN_B

SENSE

REFT_A

REFB_A

VREF

14

AVDD

ADC

VIN-_B

SHA

VIN+_B

14

D13

B

-D

0B

OEB_B

14

MUX_SELECT

AGND

DRGND

DFS

Mode

Control

+

REFT_B

REFB_B

Clock

Duty Cycle

Stabilizer

OTR_B

OTR_A

O

B

0.5V

DRVDD

Figure 1. Functional Block Diagram

PRODUCT HIGHLIGHTS

1.

Pin compatible with AD9238, 12-bit 20/40/65MSPS

ADC.

2.

Speed grade options of 20 MSPS, 40 MSPS, and 65

MSPS allow flexibility between power, cost, and

performance to suit an application.

3.

Low power consumption:

AD9248-65: 65 MSPS = 600 mW.

AD9248-40: 40 MSPS = 330 mW.

AD9248-20: 20 MSPS = 180 mW.

4.

The patented SHA input maintains excellent

performance for input frequencies up to 100 MHz and

can be configured for single-ended or differential

operation.

5.

Typical channel isolation of 85 dB @ f

IN

= 10 MHz.

6.

The clock duty cycle stabilizer (AD9248-65 only)

maintains performance over a wide range of clock

duty cycles.

7.

The OTR output bits indicate when either input signal

is beyond the selected input range.

8.

Multiplexed data output option enables single-port

operation from either data port A or data port B.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9248BST-40 | 14-Bit, 20/40/65 MSPS Dual A/ D Converter |

| AD9248BST-65 | 14-Bit, 20/40/65 MSPS Dual A/ D Converter |

| AD9260 | High-Speed Oversampling CMOS ADC with 16-Bit Resolution at a 2.5 MHz Output Word Rate |

| AD9260AS | High-Speed Oversampling CMOS ADC with 16-Bit Resolution at a 2.5 MHz Output Word Rate |

| AD9260EB | High-Speed Oversampling CMOS ADC with 16-Bit Resolution at a 2.5 MHz Output Word Rate |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9248BST-40 | 制造商:AD 制造商全稱:Analog Devices 功能描述:14-Bit, 20/40/65 MSPS Dual A/ D Converter |

| AD9248BST-64 | 制造商:Analog Devices 功能描述:- Bulk |

| AD9248BST-65 | 制造商:Analog Devices 功能描述:ADC DUAL PIPELINED 65MSPS 14BIT PARALLEL 64LQFP - Bulk |

| AD9248BST-65EB | 制造商:Analog Devices 功能描述:Evaluation Board For Dual A/D Converter ;14-Bit, 20 MSPS/40 MSPS/65 MSPS 制造商:Analog Devices 功能描述:EVAL BD FOR DUAL A/D CNVRTR ;14BIT, 20 MSPS/40 MSPS/65 MSPS - Bulk |

| AD9248BST-65EBZ | 制造商:Analog Devices 功能描述:Evaluation Board For Dual A/D Converter ;14-Bit, 20 MSPS/40 MSPS/65 MSPS 制造商:Analog Devices 功能描述:BOARD EVAL WITH AD9248BST-65 |

發布緊急采購,3分鐘左右您將得到回復。