- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373963 > AD9446-100LVDS (Analog Devices, Inc.) 16-Bit, 80/100 MSPS ADC PDF資料下載

參數(shù)資料

| 型號(hào): | AD9446-100LVDS |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 16-Bit, 80/100 MSPS ADC |

| 中文描述: | 16位,80/100 MSPS的模數(shù)轉(zhuǎn)換器 |

| 文件頁(yè)數(shù): | 24/36頁(yè) |

| 文件大小: | 952K |

| 代理商: | AD9446-100LVDS |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

AD9446

THEORY OF OPERATION

The AD9446 architecture is optimized for high speed and ease

of use. The analog inputs drive an integrated, high bandwidth

track-and-hold circuit that samples the signal prior to quantization

by the 16-bit pipeline ADC core. The device includes an on-board

reference and input logic that accepts TTL, CMOS, or LVPECL

levels. The digital output logic levels are user selectable as standard

3 V CMOS or LVDS (ANSI-644 compatible) via the OUTPUT

MODE pin.

Rev. 0 | Page 24 of 36

ANALOG INPUT AND REFERENCE OVERVIEW

A stable and accurate 0.5 V band gap voltage reference is built

into the AD9446. The input range can be adjusted by varying

the reference voltage applied to the AD9446, using either the

internal reference or an externally applied reference voltage.

The input span of the ADC tracks reference voltage changes

linearly.

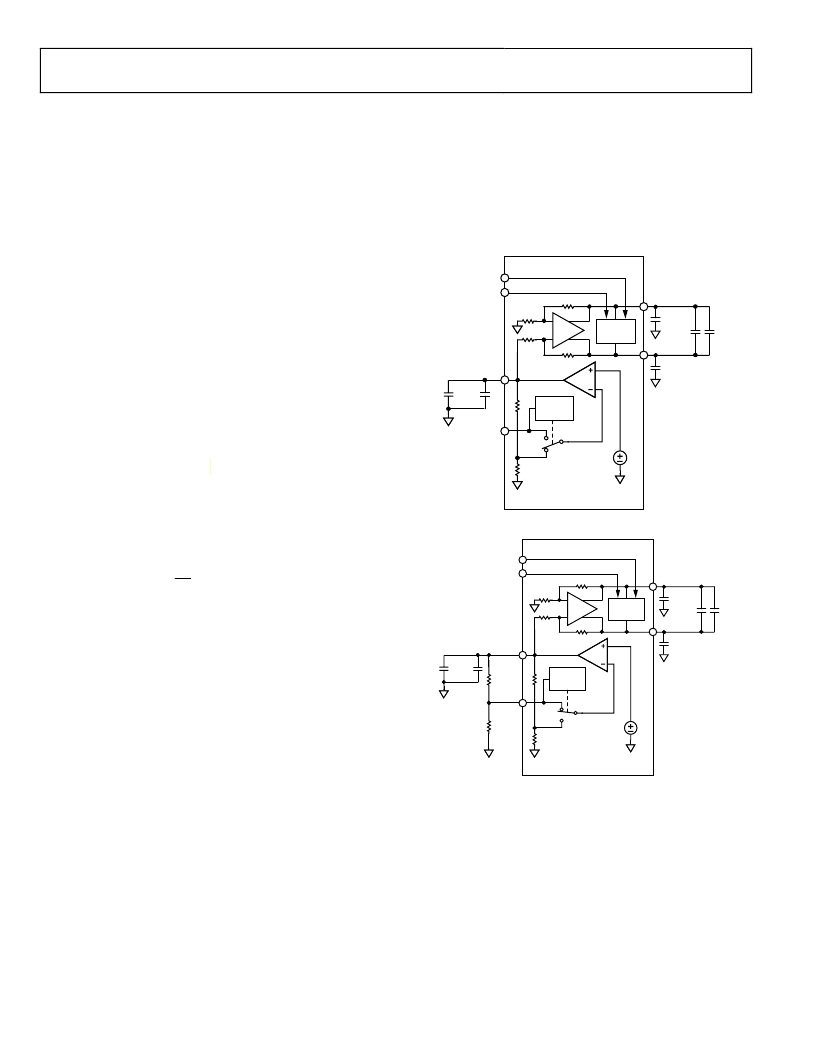

Internal Reference Connection

A comparator within the AD9446 detects the potential at the

SENSE pin and configures the reference into three possible states,

which are summarized in Table 9. If SENSE is grounded, the

reference amplifier switch is connected to the internal resistor

divider (see Figure 55), setting VREF to ~1.6 V. If a resistor

divider is connected as shown in Figure 56, the switch again sets

to the SENSE pin. This puts the reference amplifier in a

noninverting mode with the VREF output defined as

1

×

=

R1

R2

V

VREF

5

In all reference configurations, REFT and REFB drive the

analog-to-digital conversion core and establish its input span.

The input range of the ADC always equals twice the voltage at

the reference pin for either an internal or an external reference.

Internal Reference Trim

The internal reference voltage is trimmed during the production

test; therefore, there is little advantage to the user supplying an

external voltage reference to the AD9446. The gain trim is per-

formed with the AD9446 input range set to 3.2 V p-p nominal

(SENSE connected to AGND). Because of this trim and the

maximum ac performance provided by the 3.2 V p-p analog

input range, there is little benefit to using analog input ranges

<2 V p-p. However, reducing the range can improve SFDR

performance in some applications. Likewise, increasing the

range up to 3.8 V p-p can improve SNR. Users are cautioned

that the differential nonlinearity of the ADC varies with the

reference voltage. Configurations that use <2.0 V p-p may

exhibit missing codes and therefore degraded noise and

distortion performance.

10

μ

F+

0.1

μ

F

VREF

SENSE

0.5V

AD9446

VIN–

VIN+

REFT

0.1

μ

F

0.1

μ

F

10

μ

F

0.1

μ

F

REFB

SELECT

LOGIC

ADC

CORE

+

0

Figure 55. Internal Reference Configuration

0

10

μ

F+

0.1

μ

F

VREF

SENSE

R2

R1

0.5V

AD9446

VIN–

VIN+

REFT

0.1

μ

F

0.1

μ

F

10

μ

F

0.1

μ

F

REFB

SELECT

LOGIC

ADC

CORE

+

Figure 56. Programmable Reference Configuration

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9446-100PCB | 16-Bit, 80/100 MSPS ADC |

| AD9446-80LVDS | 16-Bit, 80/100 MSPS ADC |

| AD9446-80PCB | 16-Bit, 80/100 MSPS ADC |

| AD9480 | 8-Bit, 250 MSPS 3.3 V A/D Converter |

| AD9480-LVDS-PCB3 | 8-Bit, 250 MSPS 3.3 V A/D Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ad9446-100lvds/pcb | 制造商:Analog Devices 功能描述:EVAL KIT FOR 16BIT, 80/100 MSPS ADC - Bulk 制造商:Rochester Electronics LLC 功能描述: |

| AD9446100LVDS/PCBZ | 制造商:Analog Devices 功能描述:EVAL BD - Bulk |

| AD9446-100LVDSPCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:High Speed ADC USB FIFO Evaluation Kit |

| AD9446-100PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:16-Bit, 80/100 MSPS ADC |

| AD9446-80LVDS | 制造商:AD 制造商全稱:Analog Devices 功能描述:16-Bit, 80/100 MSPS ADC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。