- 您現在的位置:買賣IC網 > PDF目錄1986 > AD9484BCPZRL7-500 (Analog Devices Inc)IC ADC 8BIT 500MSPS 56LFCSP PDF資料下載

參數資料

| 型號: | AD9484BCPZRL7-500 |

| 廠商: | Analog Devices Inc |

| 文件頁數: | 1/24頁 |

| 文件大小: | 0K |

| 描述: | IC ADC 8BIT 500MSPS 56LFCSP |

| 標準包裝: | 750 |

| 位數: | 8 |

| 采樣率(每秒): | 500M |

| 數據接口: | 串行,SPI? |

| 轉換器數目: | 1 |

| 功率耗散(最大): | 720mW |

| 電壓電源: | 模擬和數字 |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 56-VFQFN 裸露焊盤,CSP |

| 供應商設備封裝: | 56-LFCSP-VQ(8x8) |

| 包裝: | 帶卷 (TR) |

| 輸入數目和類型: | 1 個差分,雙極 |

8-Bit, 500 MSPS,

1.8 V Analog-to-Digital Converter

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibilityis assumedbyAnalogDevicesforitsuse,norforanyinfringementsof patentsorother

rightsofthirdpartiesthatmayresultfromitsuse.Specificationssubjecttochangewithoutnotice.No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

2011 Analog Devices, Inc. All rights reserved.

FEATURES

SNR = 47 dBFS at fIN up to 250 MHz at 500 MSPS

ENOB of 7.5 bits at fIN up to 250 MHz at 500 MSPS (1.0 dBFS)

SFDR = 79 dBc at fIN up to 250 MHz at 500 MSPS (1.0 dBFS)

Integrated input buffer

Excellent linearity

DNL = ±0.1 LSB typical

INL = ±0.1 LSB typical

LVDS at 500 MSPS (ANSI-644 levels)

1 GHz full power analog bandwidth

On-chip reference, no external decoupling required

Low power dissipation

670 mW at 500 MSPS—LVDS SDR output

Programmable (nominal) input voltage range

1.18 V p-p to 1.6 V p-p, 1.5 V p-p nominal

1.8 V analog and digital supply operation

Selectable output data format (offset binary, twos

complement, Gray code)

Clock duty cycle stabilizer

Integrated data capture clock

APPLICATIONS

Wireless and wired broadband communications

Cable reverse path

Communications test equipment

Low cost digital oscilloscopes

Satellite subsystems

Power amplifier linearization

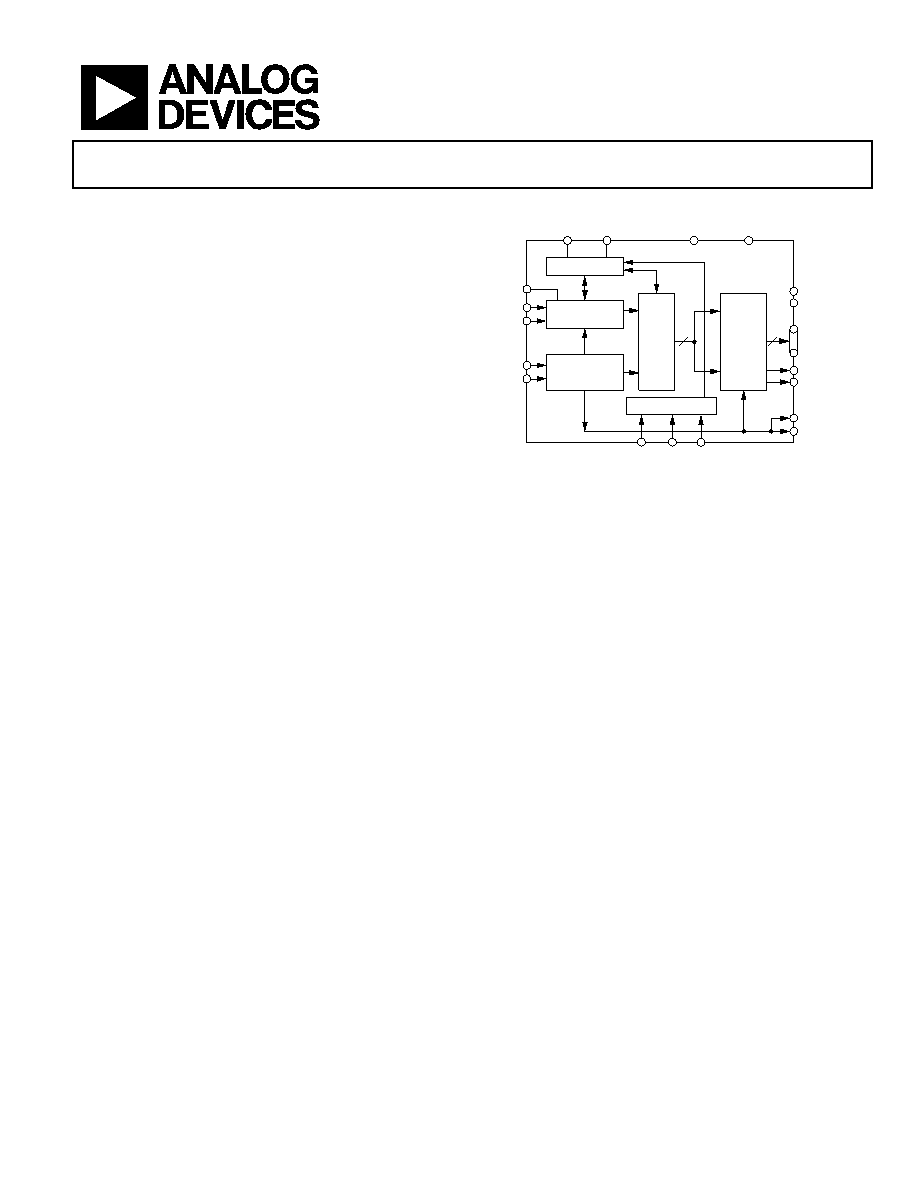

FUNCTIONAL BLOCK DIAGRAM

AGND

PWDN

VREF

AVDD

VIN+

VIN–

CML

TRACK-AND-HOLD

REFERENCE

ADC

CORE

OUTPUT

STAGING

LVDS

CLK+

CLK–

CLOCK

MANAGEMENT

SERIAL PORT

SCLK/DFS

SDIO

CSB

DCO–

DCO+

OR–

OR+

D7± TO D0±

DRGND

DRVDD

8

AD9484

09

61

5

-00

1

Figure 1.

GENERAL DESCRIPTION

The AD9484 is an 8-bit, monolithic, sampling analog-to-digital

converter (ADC) optimized for high performance, low power,

and ease of use. The part operates at up to a 500 MSPS conver-

sion rate and is optimized for outstanding dynamic performance

in wideband carrier and broadband systems. All necessary

functions, including a sample-and-hold and voltage reference,

are included on the chip to provide a complete signal conversion

solution. The VREF pin can be used to monitor the internal

reference or provide an external voltage reference (external

reference mode must be enabled through the SPI port).

The ADC requires a 1.8 V analog voltage supply and a differen-

tial clock for full performance operation. The digital outputs are

LVDS (ANSI-644) compatible and support twos complement,

offset binary format, or Gray code. A data clock output is available

for proper output data timing.

Fabricated on an advanced BiCMOS process, the AD9484 is availa-

ble in a 56-lead LFCSP, and is specified over the industrial

temperature range (40°C to +85°C). This product is protected

by a U.S. patent.

PRODUCT HIGHLIGHTS

1.

High Performance.

Maintains 47 dBFS SNR at 500 MSPS with a 250 MHz input.

2.

Ease of Use.

LVDS output data and output clock signal allow interface

to current FPGA technology. The on-chip reference and

sample-and-hold provide flexibility in system design. Use

of a single 1.8 V supply simplifies system power supply design.

3.

Serial Port Control.

Standard serial port interface supports various product

functions, such as data formatting, power-down, gain

adjust, and output test pattern generation.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9510BCPZ-REEL7 | IC CLOCK DIST 8OUT PLL 64LFCSP |

| AD9511BCPZ-REEL7 | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9512UCPZ-EP-R7 | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9512UCPZ-EP | IC CLOCK DIST 5OUT PLL 48LFCSP |

| AD9513BCPZ-REEL7 | IC CLOCK DIST 3OUT PLL 32LFCSP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9500 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Digitally Programmable Delay Generator |

| AD9500BP | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD9500BP-REEL | 制造商:Analog Devices 功能描述:Digitally Programmable Delay Generator 28-Pin PLCC T/R |

| AD9500BQ | 制造商:AD 制造商全稱:Analog Devices 功能描述:Digitally Programmable Delay Generator |

| AD9500TE | 制造商:AD 制造商全稱:Analog Devices 功能描述:Digitally Programmable Delay Generator |

發布緊急采購,3分鐘左右您將得到回復。