- 您現在的位置:買賣IC網 > PDF目錄1987 > AD9540BCPZ-REEL7 (Analog Devices Inc)IC CLOCK GEN/SYNTHESIZER 48LFCSP PDF資料下載

參數資料

| 型號: | AD9540BCPZ-REEL7 |

| 廠商: | Analog Devices Inc |

| 文件頁數: | 1/32頁 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN/SYNTHESIZER 48LFCSP |

| 標準包裝: | 750 |

| 類型: | 時鐘發生器 |

| PLL: | 是 |

| 輸入: | 時鐘 |

| 輸出: | CML,PECL |

| 電路數: | 1 |

| 比率 - 輸入:輸出: | 2:2 |

| 差分 - 輸入:輸出: | 是/是 |

| 頻率 - 最大: | 655MHz |

| 除法器/乘法器: | 是/無 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 48-VFQFN 裸露焊盤,CSP |

| 供應商設備封裝: | 48-LFCSP-VQ(7x7) |

| 包裝: | 帶卷 (TR) |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

655 MHz Low Jitter Clock Generator

AD9540

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibilityis assumedbyAnalogDevicesforitsuse,norforanyinfringements of patents or other

rightsofthirdpartiesthatmayresultfromitsuse.Specificationssubjecttochangewithoutnotice.No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

2006 Analog Devices, Inc. All rights reserved.

FEATURES

Excellent intrinsic jitter performance

200 MHz phase frequency detector inputs

655 MHz programmable input dividers for the phase

frequency detector (÷M, ÷N) {M, N = 1 to 16} (bypassable)

Programmable RF divider (÷R) {R = 1, 2, 4, 8} (bypassable)

8 programmable phase/frequency profiles

400 MSPS internal DDS clock speed

48-bit frequency tuning word resolution

14-bit programmable phase offset

1.8 V supply for device operation

3.3 V supply for I/O, CML driver, and charge pump output

Software controlled power-down

48-lead LFCSP_VQ package

Programmable charge pump current (up to 4 mA)

Dual-mode PLL lock detect

655 MHz CML-mode PECL-compliant output driver

APPLICATIONS

Clocking high performance data converters

Base station clocking applications

Network (SONET/SDH) clocking

Gigabit Ethernet (GbE) clocking

Instrumentation clocking circuits

Agile LO frequency synthesis

Automotive radar

FM chirp source for radar and scanning systems

Test and measurement equipment

Acousto-optic device drivers

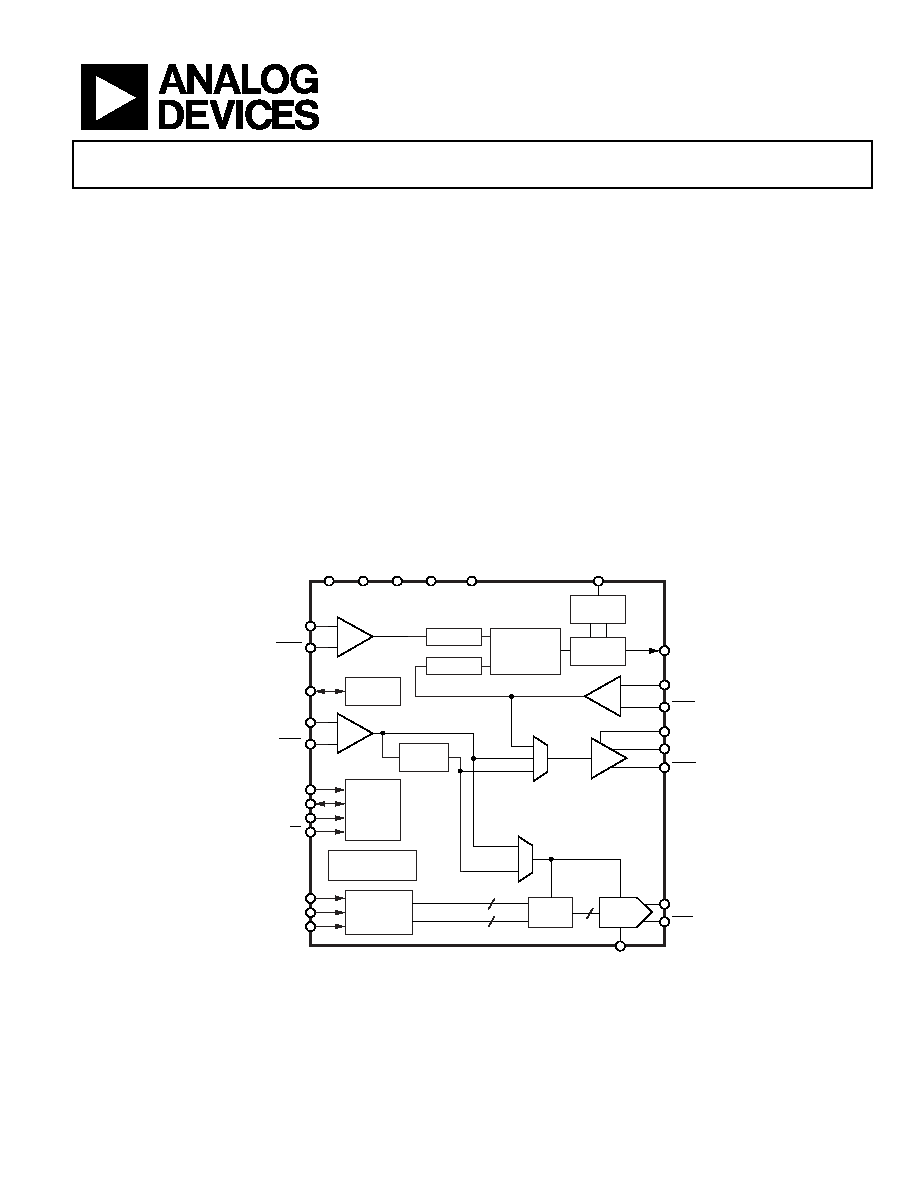

FUNCTIONAL BLOCK DIAGRAM

AVDD AGND DVDD DGND

CP_VDD

CP_RSET

CP

REF, AMP

REFIN

CLK1

CHARGE

PUMP

PHASE

FREQUENCY

DETECTOR

M DIVIDER

N DIVIDER

DIVIDER

1, 2, 4, 8

SYNC_IN/STATUS

SYNC, PLL

LOCK

SCLK

SDI/O

SDO

CS

SERIAL

CONTROL

PORT

TIMING AND

CONTROL LOGIC

CLK2

CP_OUT

CLK2

DRV_RSET

OUT0

CML

OUT0

CLK

DIVCLK

S2

S1

S0

PHASE/

FREQUENCY

PROFILES

DDS

IOUT

DAC

DAC_RSET

48

10

14

04947-001

AD9540

Figure 1.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9547BCPZ-REEL7 | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| AD9548BCPZ-REEL7 | IC CLOCK GEN/SYNCHRONIZR 88LFCSP |

| AD9549ABCPZ-REEL7 | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| AD9550BCPZ-REEL7 | IC INTEGER-N TRANSLATOR 32-LFCSP |

| AD9551BCPZ | IC CLOCK GEN MULTISERV 40-LFCSP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9540PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:655 MHz Low Jitter Clock Generator |

| AD9540-VCO/PCB | 制造商:Analog Devices 功能描述:EVAL BD FOR AD9540 ,655 MHZ LOW JITTER CLOCK GEN - Trays |

| AD9540-VCO/PCBZ | 功能描述:BOARD EVAL CLK GEN SYNTH 48LFCSP RoHS:是 類別:編程器,開發系統 >> 評估演示板和套件 系列:- 標準包裝:1 系列:- 主要目的:電信,線路接口單元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要屬性:T1/J1/E1 LIU 次要屬性:- 已供物品:板,電源,線纜,CD 其它名稱:82EBV2081 |

| AD9542/PCBZ | |

| AD9542BCPZ | 功能描述:SYNCHRONIZER & ADAPTIVE CLOCK TR 制造商:analog devices inc. 系列:* 包裝:托盤 零件狀態:在售 安裝類型:表面貼裝 封裝/外殼:64-WFQFN 裸露焊盤 供應商器件封裝:64-LFCSP(9x9) 標準包裝:1 |

發布緊急采購,3分鐘左右您將得到回復。