- 您現在的位置:買賣IC網 > PDF目錄373965 > AD96698 (Analog Devices, Inc.) Ultrafast TTL Comparators(超快比較器) PDF資料下載

參數資料

| 型號: | AD96698 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Ultrafast TTL Comparators(超快比較器) |

| 中文描述: | 超快的TTL比較器(超快比較器) |

| 文件頁數: | 4/8頁 |

| 文件大小: | 142K |

| 代理商: | AD96698 |

AD9696/AD9698

–4–

REV. B

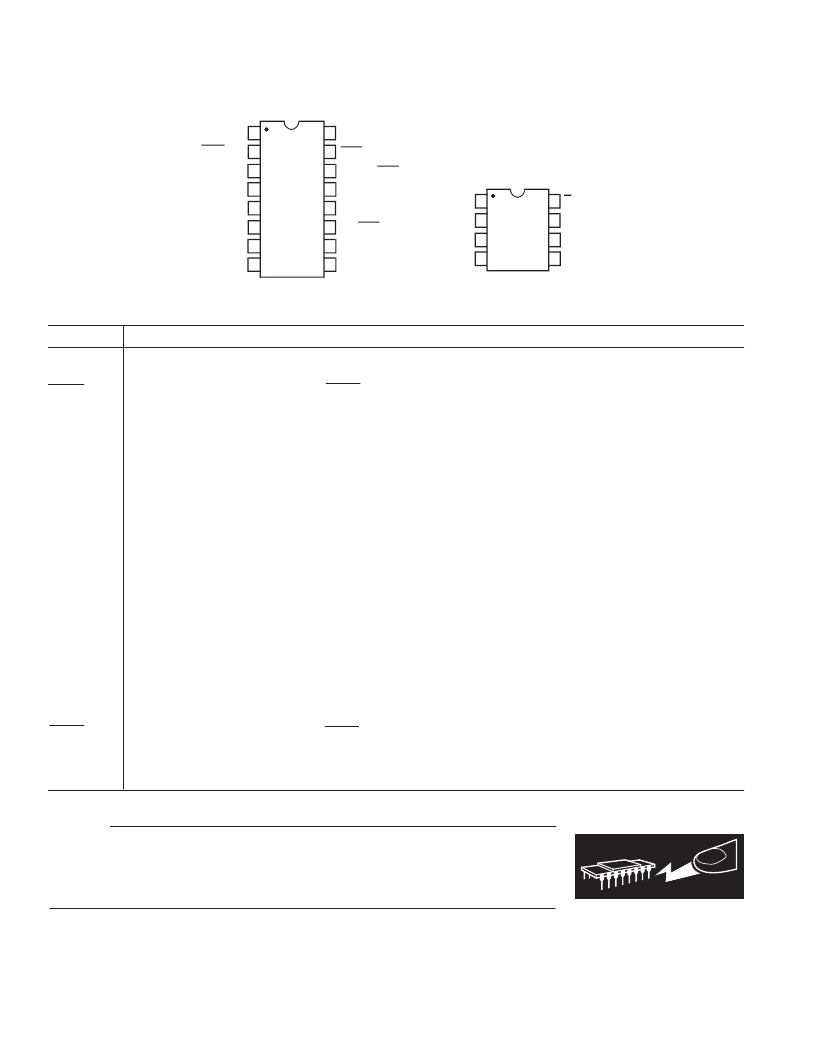

PIN CONFIGURAT IONS

AD9696KN/KR/KQ/TQ/TZ

Q1

OUT

(N/C)

Q1

OUT

(–V

S

)

GROUND (–IN

1

)

LATCH ENABLE 1 (+IN

1

)

N/C (+IN

2

)

–V

S

(–IN

2

)

–IN

1

(+V

S

)

TOP VIEW

(Not to Scale)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

16

15

+IN

1

(N/C)

+IN

2

(LATCH ENABLE 2)

–IN

2

(GROUND)

N/C (Q2

OUT

)

LATCH ENABLE 2 (Q1

OUT

)

Q2

OUT

(GROUND)

Q2

OUT

(LATCH ENABLE 1)

AD9698KN/KQ/TQ

[AD9698KR/TZ PINOUTS SHOWN IN ( )]

GROUND (Q1

OUT

)

+V

S

(Q2

OUT

)

LATCH

ENABLE

1

2

3

4

TOP VIEW

(Not to Scale)

5

6

7

8

+V

S

+IN

–IN

–V

S

GROUND

Q

OUT

Q

OUT

Name

Function

Q1

OUT

One of two complementary outputs. Q1

OUT

will be at logic HIGH if voltage at +IN

1

is greater than voltage at

–IN

1

and LAT CH ENABLE 1 is at logic LOW.

One of two complementary outputs. Q1

OUT

will be at logic HIGH if voltage at –IN

1

is greater than voltage at

+IN

1

and LAT CH ENABLE 1 is at logic LOW.

Analog and digital ground return. All GROUND pins should be connected together and to a low impedance

ground plane near the comparator.

Output at Q1

OUT

will track differential changes at the inputs when LAT CH ENABLE 1 is at logic LOW.

When LAT CH ENABLE 1 is at logic HIGH, the output at Q1

OUT

will reflect the input state at the application of

the latch command, delayed by the Latch Enable Setup T ime (t

S

). Since the architecture of the input stage (see

block diagram) is faster than the logic of the latch stage, data will typically be latched if applied to the comparator(s)

within 1.7 ns after the latch. T his is the Setup T ime (t

S

); for guaranteed performance, t

S

must be 3 ns.

No internal connection to comparator.

Negative power supply connection; nominally –5.2 V.

Inverting input of differential input stage for Comparator #1.

Noninverting input of differential input stage for Comparator #1.

Noninverting input of differential input stage for Comparator #2.

Inverting input of differential input stage for Comparator #2.

Positive power supply connection; nominally +5 V.

Output at Q2

OUT

will track differential changes at the inputs when LAT CH ENABLE 2 is at logic LOW.

When LAT CH ENABLE 2 is at logic HIGH, the output at Q2

OUT

will reflect the input state at the application of

the latch command, delayed by the Latch Enable Setup T ime (t

S

). Since the architecture of the input stage (see

block diagram) is faster than the logic of the latch stage, data will typically be latched if applied to the comparator(s)

within 1.7 ns after the latch. T his is the Setup T ime (t

S

); for guaranteed performance, t

S

must be 3 ns.

One of two complementary outputs. Q2

OUT

will be at logic HIGH if voltage at –IN

2

is greater than voltage at

+IN

2

and LAT CH ENABLE 2 is at logic LOW.

One of two complementary outputs. Q2

OUT

will be at logic HIGH if voltage at +IN

2

is greater than voltage at

–IN

2

and LAT CH ENABLE 2 is at logic LOW.

Q1

OUT

GROUND

LAT CH

ENABLE 1

N/C

–V

S

–IN

1

+IN

1

+IN

2

–IN

2

+V

S

LAT CH

ENABLE 2

Q2

OUT

Q2

OUT

WARNING!

ESD SENSITIVE DEVICE

C AUT ION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD9696/AD9698 features proprietary ESD protection circuitry, permanent dam-

age may occur on devices subjected to high energy electrostatic discharges. T herefore, proper

ESD precautions are recommended to avoid performance degradation or loss of functionality.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9696TQ | Ultrafast TTL Comparators |

| AD9698KN | Ultrafast TTL Comparators |

| AD9698KQ | Ultrafast TTL Comparators |

| AD9698KR | Ultrafast TTL Comparators |

| AD9698TQ | Ultrafast TTL Comparators |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9670BBCZ | 功能描述:ADC / DAC多通道 14 Bit Octal BiCMOS AFE w/Dig Demod RoHS:否 制造商:Texas Instruments 轉換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-40 |

| AD9670EBZ | 功能描述:數據轉換 IC 開發工具 14 Bit Octal BiCMOS AFE w/Dig Demod RoHS:否 制造商:Texas Instruments 產品:Demonstration Kits 類型:ADC 工具用于評估:ADS130E08 接口類型:SPI 工作電源電壓:- 6 V to + 6 V |

| AD9671KBCZ | 功能描述:8 Channel AFE 14 Bit 150mW 144-CSPBGA (10x10) 制造商:analog devices inc. 系列:- 包裝:托盤 零件狀態:有效 位數:14 通道數:8 功率(W):150mW 電壓 - 電源,模擬:- 電壓 - 電源,數字:- 封裝/外殼:- 供應商器件封裝:144-CSPBGA(10x10) 標準包裝:1 |

| AD9674 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Octal Ultrasound AFE with Digital Demodulator |

| AD9674EBZ | 功能描述:數據轉換 IC 開發工具 14Bit BiCMOS Octal AFE w/LVDS output RoHS:否 制造商:Texas Instruments 產品:Demonstration Kits 類型:ADC 工具用于評估:ADS130E08 接口類型:SPI 工作電源電壓:- 6 V to + 6 V |

發布緊急采購,3分鐘左右您將得到回復。