- 您現在的位置:買賣IC網 > PDF目錄373975 > ADAU1592ASVZ (ANALOG DEVICES INC) Class-D Audio Power Amplifier PDF資料下載

參數資料

| 型號: | ADAU1592ASVZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 音頻/視頻放大 |

| 英文描述: | Class-D Audio Power Amplifier |

| 中文描述: | 24 W, 2 CHANNEL, AUDIO AMPLIFIER, PQFP48 |

| 封裝: | ROHS COMPLIANT, MS-026ABC, TQFP-48 |

| 文件頁數: | 18/24頁 |

| 文件大小: | 457K |

| 代理商: | ADAU1592ASVZ |

ADAU1592

POWER-UP/POWER-DOWN SEQUENCE

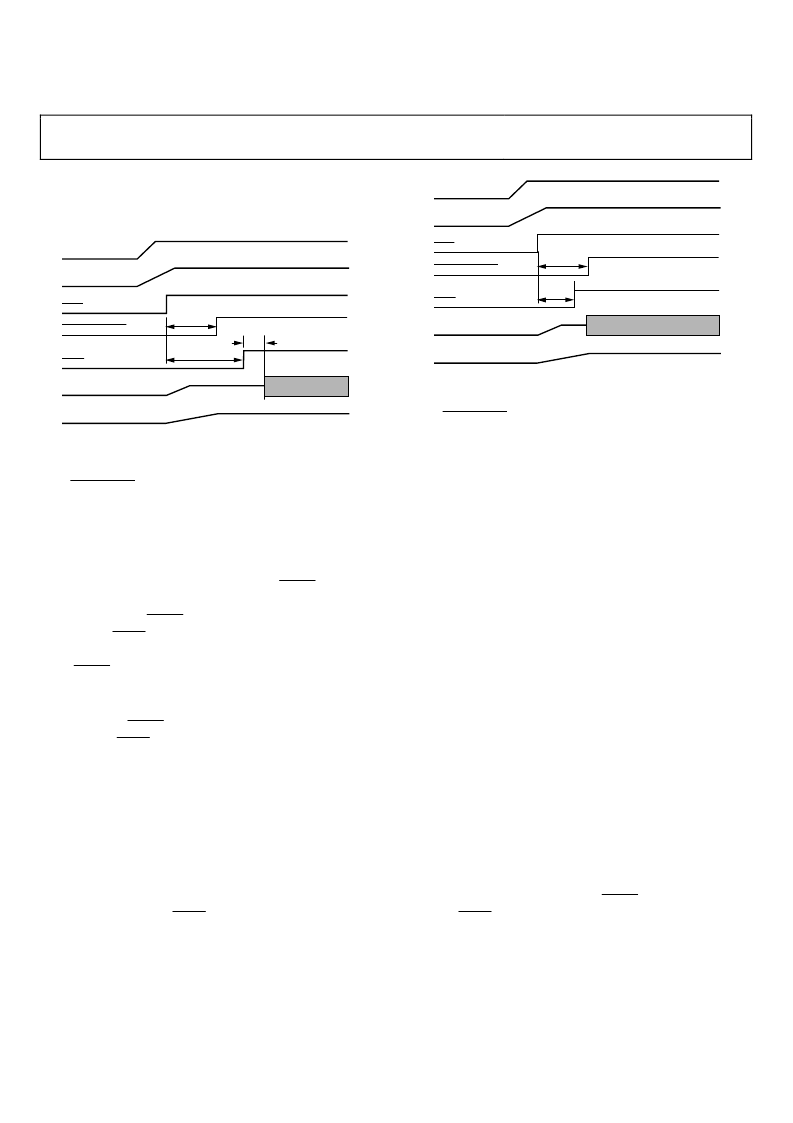

Figure 46 shows the recommended power-up sequence for the

ADAU1592.

Rev. 0 | Page 18 of 24

0

AVDD/DVDD

PVDD

STDN

MUTE

OUTx+/OUTx–

PVDD/2

AINx

AVDD/2

t

PDL-H

t

INT

t

WAIT

t

INT

= 650ms @ 24.576MHz CLOCK

t

PDL-H

= 200μs

t

WAIT

= 10 × R

IN

× C

IN

INTERNAL MUTE

NOTES

1. INTERNAL MUTE IS INTERNAL TO CHIP.

Figure 46. Recommended Power-Up Sequence

The ADAU1592 has a special turn-on sequence that consists of

a fixed internal mute time during which the power stage does

not start switching. This internal mute time depends on the

master clock frequency and is 650 ms for a 24.576 MHz clock.

Also, the internal mute overrides the external MUTE and

ensures that the power stage does not switch on immediately

even if the external MUTE signal is pulled high in less than

650 ms after STDN. The power stage starts switching only after

650 ms plus a small propagation delay of 200 μs has elapsed and

after MUTE is deasserted. Therefore, it is recommended to

ensure that t

WAIT

> t

INT

to prevent the pop and click during

power-on.

Ensure that the MUTE signal is delayed by at least t

WAIT

seconds after STDN. This time is approximately 10 times the

charging time constant of the input coupling capacitor.

For example, if the input coupling capacitor is 4.7 μF, the time

constant is

T

=

R

×

C

= 20 kΩ × 4.7 μF = 94 ms

Therefore,

t

WAIT

= 10 ×

T

= 940 ms ~ 1 sec.

t

WAIT

is needed to ensure that the input capacitors are charged to

AVDD/2 before turning on the power stage.

When t

WAIT

< t

INT

, the power stage does not start switching until

650 ms has elapsed after STDN (see Figure 47). However, note

that this method does not ensure pop-and-click suppression

because of less than recommended or insufficient t

WAIT

t

INT

= 650ms @ 24.576MHz CLOCK

t

WAIT

< T

INT

0

AVDD/DVDD

PVDD

STDN

MUTE

OUTx+/OUTx–

PVDD/2

AINx

AVDD/2

t

INT

t

WAIT

INTERNAL MUTE

NOTES

1. INTERNAL MUTE IS INTERNAL TO CHIP.

Figure 47. Power-Up Sequence, t

WAIT

< t

INT

The ADAU1592 uses three separate supplies: AVDD (3.3 V

analog for PGA and modulator), DVDD (3.3 V digital for

control logic and clock oscillator), and PVDD (9 V to 18 V

power stage and level shifter). Separate pins are provided for

the AVDD, DVDD, and PVDD supply connections, as well as

AGND, DGND, and PGND.

In addition, the ADAU1592 incorporates a built-in undervolt-

age lockout logic on DVDD as well as PVDD. This helps detect

undervoltage operation and eliminates the need to have an external

mechanism to sense the supplies.

The ADAU1592 monitors the DVDD and PVDD supply voltages

and prevents the power stage from turning on if either of the

supplies are not present or are below the operating threshold.

Therefore, if DVDD is missing or below the operating thresh-

old, for example, the power stage does not turn on, even if

PVDD is present, or vice versa.

Because this protection is only present on DVDD and PVDD

and not on AVDD, shorting both AVDD and DVDD externally

or generating AVDD and DVDD from one power source is

recommended. This ensures that both AVDD and DVDD

supplies are tracking each other and avoids the need to monitor

the sequence with respect to PVDD. This also ensures minimal

pop and click during power-up.

When using separate AVDD and DVDD supplies, ensure that

both supplies are stable before unmuting or turning on the

power stage.

Similarly, during shutdown, pulling MUTE to logic low before

pulling STDN down is recommended. However, where a fault

event occurs, the power stage shuts down to protect the part. In

this case, depending on the signal level, there is some pop at the

speaker.

相關PDF資料 |

PDF描述 |

|---|---|

| ADAU1592ASVZ-RL | Class-D Audio Power Amplifier |

| ADAU1592ASVZ-RL7 | Class-D Audio Power Amplifier |

| ADAU1702 | SigmaDSP 28-56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1702JSTZ | SigmaDSP 28-56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1702JSTZ-RL | SigmaDSP 28-56-Bit Audio Processor with Two ADCs and Four DACs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADAU1592ASVZ-RL | 制造商:Analog Devices 功能描述: |

| ADAU1592ASVZ-RL7 | 制造商:Analog Devices 功能描述: |

| ADAU1701 | 制造商:AD 制造商全稱:Analog Devices 功能描述:SigmaDSP 28/56-Bit Audio Processor with 2ADC/4DAC |

| ADAU1701JSTZ | 功能描述:IC AUDIO PROC 2ADC/4DAC 48-LQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 音頻處理 系列:SigmaDSP® 其它有關文件:STA321 View All Specifications 標準包裝:1 系列:Sound Terminal™ 類型:音頻處理器 應用:數字音頻 安裝類型:表面貼裝 封裝/外殼:64-LQFP 裸露焊盤 供應商設備封裝:64-LQFP EP(10x10) 包裝:Digi-Reel® 其它名稱:497-11050-6 |

| ADAU1701JSTZ-RL | 功能描述:IC AUDIO PROC 2ADC/4DAC 48-LQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 音頻處理 系列:SigmaDSP® 其它有關文件:STA321 View All Specifications 標準包裝:1 系列:Sound Terminal™ 類型:音頻處理器 應用:數字音頻 安裝類型:表面貼裝 封裝/外殼:64-LQFP 裸露焊盤 供應商設備封裝:64-LQFP EP(10x10) 包裝:Digi-Reel® 其它名稱:497-11050-6 |

發布緊急采購,3分鐘左右您將得到回復。