- 您現在的位置:買賣IC網 > PDF目錄373977 > ADCMP573BCP-R2 (ANALOG DEVICES INC) Ultrafast 3.3 V/5 V Single-Supply SiGe Comparators PDF資料下載

參數資料

| 型號: | ADCMP573BCP-R2 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 運動控制電子 |

| 英文描述: | Ultrafast 3.3 V/5 V Single-Supply SiGe Comparators |

| 中文描述: | COMPARATOR, 5000 uV OFFSET-MAX, 0.165 ns RESPONSE TIME, QCC16 |

| 封裝: | 3 X 3 MM, MO-220-VEED-2, LFCSP-16 |

| 文件頁數: | 13/16頁 |

| 文件大小: | 381K |

| 代理商: | ADCMP573BCP-R2 |

ADCMP572/ADCMP573

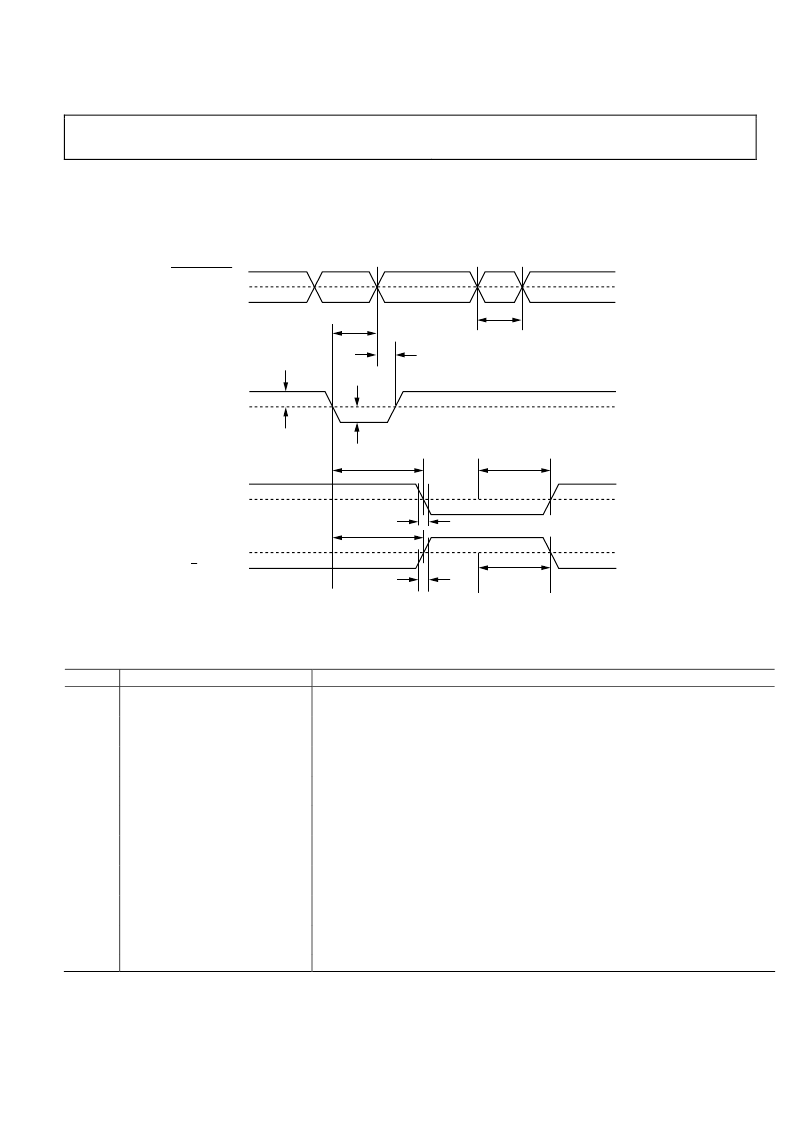

TIMING INFORMATION

Figure 29 illustrates the ADCMP572/ADCMP573 compare and latch timing relationships. Table 4 provides definitions of the terms

shown in the figure.

Rev. 0 | Page 13 of 16

50%

50%

V

N

± V

OS

50%

DIFFERENTIAL

INPUT VOLTAGE

LATCH ENABLE

Q OUTPUT

Q OUTPUT

LATCH ENABLE

t

H

t

PDL

t

PDH

t

PLOH

t

PLOL

t

R

t

F

V

IN

V

OD

t

S

t

PL

0

Figure 29. System Timing Diagram

Table 4. Timing Descriptions

Symbol

Timing

t

PDH

Input to output high delay

Description

Propagation delay measured from the time the input signal crosses the reference (± the

input offset voltage) to the 50% point of an output low-to-high transition.

Propagation delay measured from the time the input signal crosses the reference (± the

input offset voltage) to the 50% point of an output high-to-low transition.

Propagation delay measured from the 50% point of the latch enable signal low-to-high

transition to the 50% point of an output low-to-high transition.

Propagation delay measured from the 50% point of the latch enable signal low-to-high

transition to the 50% point of an output high-to-low transition.

Minimum time after the negative transition of the latch enable signal that the input signal

must remain unchanged to be acquired and held at the outputs.

Minimum time that the latch enable signal must be high to acquire an input signal

change.

Minimum time before the negative transition of the latch enable signal that an input

signal change must be present to be acquired and held at the outputs.

Amount of time required to transition from a low to a high output as measured at the

20% and 80% points.

Amount of time required to transition from a high to a low output as measured at the

20% and 80% points.

Difference between the input voltages V

A

and V

B

.

t

PDL

Input to output low delay

t

PLOH

Latch enable to output high delay

t

PLOL

Latch enable to output low delay

t

H

Minimum hold time

t

PL

Minimum latch enable pulse width

t

S

Minimum setup time

t

R

Output rise time

t

F

Output fall time

V

OD

Voltage overdrive

相關PDF資料 |

PDF描述 |

|---|---|

| ADCMP573BCP-RL7 | Ultrafast 3.3 V/5 V Single-Supply SiGe Comparators |

| ADCMP573BCP-WP | Ultrafast 3.3 V/5 V Single-Supply SiGe Comparators |

| ADCMP572 | Ultrafast 3.3 V Single-Supply Comparators |

| ADCMP572BCP | Ultrafast 3.3 V Single-Supply Comparators |

| ADCMP573 | Ultrafast 3.3 V Single-Supply Comparators |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADCMP573BCPRL7 | 制造商:AD 功能描述:NEW |

| ADCMP573BCP-RL7 | 制造商:Analog Devices 功能描述:Comparator Single 5.4V 16-Pin LFCSP EP T/R |

| ADCMP573BCP-WP | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述:Single Supply, PECL on XFCB3.0-WAFFLE PA |

| ADCMP573BCPZ-R2 | 功能描述:IC COMPARATOR PECL 3.3-5 16LFCSP RoHS:是 類別:集成電路 (IC) >> 線性 - 比較器 系列:- 標準包裝:1 系列:- 類型:通用 元件數:1 輸出類型:CMOS,開路集電極,TTL 電壓 - 電源,單路/雙路(±):2.7 V ~ 5.5 V 電壓 - 輸入偏移(最小值):7mV @ 5V 電流 - 輸入偏壓(最小值):0.25µA @ 5V 電流 - 輸出(標準):84mA @ 5V 電流 - 靜態(最大值):120µA CMRR, PSRR(標準):- 傳輸延遲(最大):600ns 磁滯:- 工作溫度:-40°C ~ 85°C 封裝/外殼:SC-74A,SOT-753 安裝類型:表面貼裝 包裝:剪切帶 (CT) 產品目錄頁面:1268 (CN2011-ZH PDF) 其它名稱:*LMV331M5*LMV331M5/NOPBLMV331M5CT |

| ADCMP573BCPZ-RL7 | 功能描述:IC COMPARATOR PECL 3.3-5 16LFCSP RoHS:是 類別:集成電路 (IC) >> 線性 - 比較器 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:- 類型:通用 元件數:1 輸出類型:CMOS,推挽式,滿擺幅,TTL 電壓 - 電源,單路/雙路(±):2.5 V ~ 5.5 V,±1.25 V ~ 2.75 V 電壓 - 輸入偏移(最小值):5mV @ 5.5V 電流 - 輸入偏壓(最小值):1pA @ 5.5V 電流 - 輸出(標準):- 電流 - 靜態(最大值):24µA CMRR, PSRR(標準):80dB CMRR,80dB PSRR 傳輸延遲(最大):450ns 磁滯:±3mV 工作溫度:-40°C ~ 85°C 封裝/外殼:6-WFBGA,CSPBGA 安裝類型:表面貼裝 包裝:管件 其它名稱:Q3554586 |

發布緊急采購,3分鐘左右您將得到回復。