- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373977 > ADCMP580BCP-R2 (ANALOG DEVICES INC) Ultrafast SiGe Voltage Comparators PDF資料下載

參數(shù)資料

| 型號(hào): | ADCMP580BCP-R2 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 運(yùn)動(dòng)控制電子 |

| 英文描述: | Ultrafast SiGe Voltage Comparators |

| 中文描述: | COMPARATOR, 10000 uV OFFSET-MAX, 0.18 ns RESPONSE TIME, QCC16 |

| 封裝: | 3 X 3 MM, MO-220VEED-2, LFCSP-16 |

| 文件頁(yè)數(shù): | 11/16頁(yè) |

| 文件大小: | 284K |

| 代理商: | ADCMP580BCP-R2 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

ADCMP580/ADCMP581/ADCMP582

APPLICATION INFORMATION

POWER/GROUND LAYOUT AND BYPASSING

The ADCMP58x family of comparators is designed for very

high speed applications. Consequently, high speed design

techniques must be used to achieve the specified performance.

It is critically important to use low impedance supply planes,

particularly for the negative supply (V

EE

), the output supply

plane (V

CCO

), and the ground plane (GND). Individual supply

planes are recommended as part of a multilayer board. Provid-

ing the lowest inductance return path for the switching currents

ensures the best possible performance in the target application.

Rev. 0 | Page 11 of 16

It is also important to adequately bypass the input and output

supplies. A 1 μF electrolytic bypass capacitor should be placed

within several inches of each power supply pin to ground. In

addition, multiple high quality 0.1 μF bypass capacitors should

be placed as close as possible to each of the V

EE

,

V

CCI

,

and

V

CCO

supply pins and should be connected to the GND plane with

redundant vias. High frequency bypass capacitors should be

carefully selected for minimum inductance and ESR. Parasitic

layout inductance should be strictly avoided to maximize the

effectiveness of the bypass at high frequencies.

ADCMP58x FAMILY OF OUTPUT STAGES

Specified propagation delay dispersion performance is achieved

by using proper transmission line terminations. The outputs of

the ADCMP580 family comparators are designed to directly

drive 400 mV into 50 Ω cable or microstrip/stripline transmis-

sion lines terminated with 50 Ω referenced to the proper return.

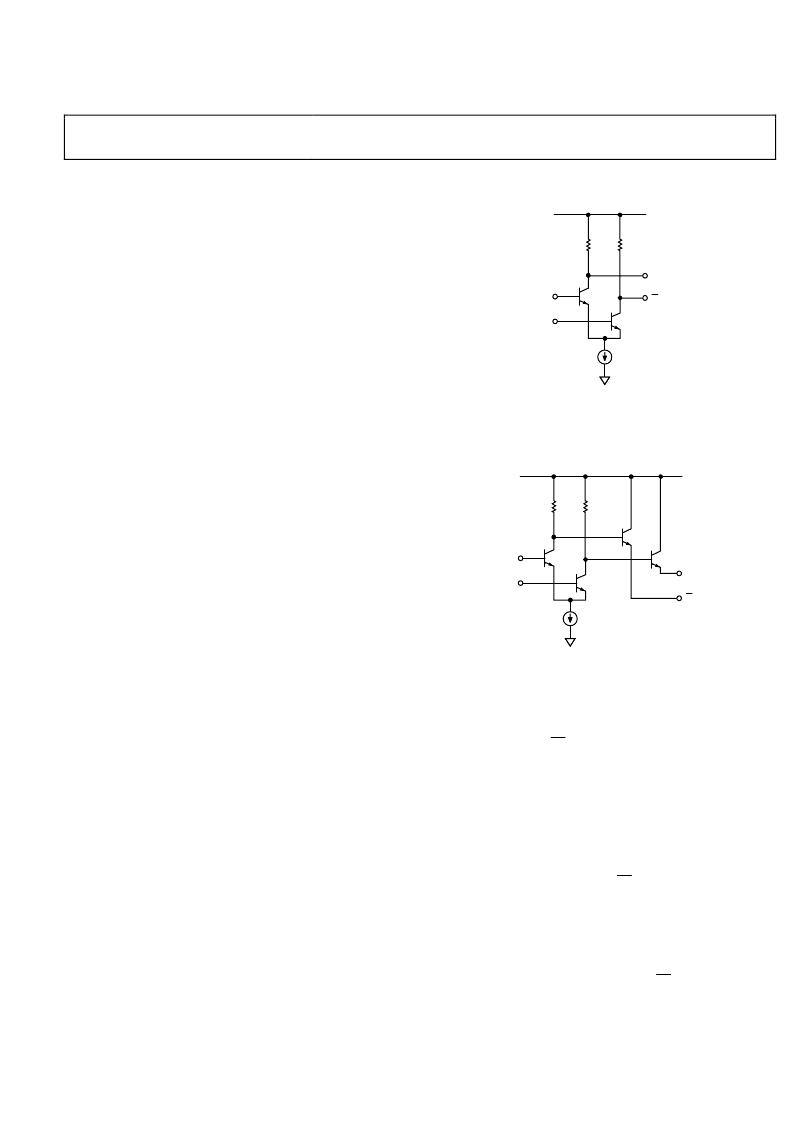

The CML output stage is shown in the simplified schematic

diagram in Figure 24. Each output is back-terminated with

50 Ω for best transmission line matching. The outputs of the

ADCMP581/ADCMP582 are illustrated in Figure 25; they

should be terminated to 2 V for ECL outputs of ADCMP581

and V

CCO

2 V for PECL outputs of ADCMP582. As an alter-

native, Thevenin equivalent termination networks may also be

used. If these high speed signals must be routed more than a

centimeter, then either microstrip or stripline techniques are

required to ensure proper transition times and to prevent

excessive output ringing and pulse width-dependent

propagation delay dispersion.

Q

16mA

50

Ω

50

Ω

Q

0

GND

V

EE

Figure 24. Simplified Schematic Diagram

of the ADCMP580 CML Output Stage

0

GND / Vcco

V

EE

Q

Q

Figure 25. Simplified Schematic Diagram of the

ADCMP581/ADCMP582 ECL/PECL Output Stage

USING/DISABLING THE LATCH FEATURE

The latch inputs (LE/LE) are active low for latch mode and are

internally terminated with 50 Ω resistors to the V

TT

pin. When

using the ADCMP580, V

TT

should be connected to ground.

When using the ADCMP581, V

TT

should be connected to

2 V. When using the ADCMP582, V

TT

should be connected

externally to V

CCO

2 V, preferably with its own low inductance

plane.

When using the ADCMP580/ADCMP582, the latch function

can be disabled by connecting the LE pin to V

EE

with an

external pull-down resistor and leaving the LE pin discon-

nected. To prevent excessive power dissipation, the resistor

should be 1.5 kΩ for the ADCMP580 and 1 kΩ for the

ADCMP582. When using the ADCMP581 comparators, the

latch can be disabled by connecting the LE pin to GND with

an external 450 Ω resistor and leaving the LE pin disconnected.

The idea is to create an approximate 0.5 V offset using the

internal resistor as half of the voltage divider. The V

TT

pin

should be connected as recommended.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADCMP580BCP-RL7 | Ultrafast SiGe Voltage Comparators |

| ADCMP580BCP-WP | Ultrafast SiGe Voltage Comparators |

| ADCMP581 | Ultrafast SiGe Voltage Comparators |

| ADCMP581BCP-R2 | Ultrafast SiGe Voltage Comparators |

| ADCMP581BCP-RL7 | Ultrafast SiGe Voltage Comparators |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADCMP580BCP-RL7 | 制造商:Analog Devices 功能描述:Comparator Single ±5.5V 16-Pin LFCSP EP T/R |

| ADCMP580BCP-WP | 制造商:Analog Devices 功能描述:Comparator Single ±5.5V 16-Pin LFCSP EP 制造商:Analog Devices 功能描述:IC ((NS)) |

| ADCMP580BCPZ-R2 | 功能描述:IC COMPARATOR CML UFAST 16-LFCSP RoHS:是 類別:集成電路 (IC) >> 線性 - 比較器 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:- 類型:通用 元件數(shù):1 輸出類型:CMOS,推挽式,滿擺幅,TTL 電壓 - 電源,單路/雙路(±):2.5 V ~ 5.5 V,±1.25 V ~ 2.75 V 電壓 - 輸入偏移(最小值):5mV @ 5.5V 電流 - 輸入偏壓(最小值):1pA @ 5.5V 電流 - 輸出(標(biāo)準(zhǔn)):- 電流 - 靜態(tài)(最大值):24µA CMRR, PSRR(標(biāo)準(zhǔn)):80dB CMRR,80dB PSRR 傳輸延遲(最大):450ns 磁滯:±3mV 工作溫度:-40°C ~ 85°C 封裝/外殼:6-WFBGA,CSPBGA 安裝類型:表面貼裝 包裝:管件 其它名稱:Q3554586 |

| ADCMP580BCPZ-RL7 | 功能描述:IC COMPARATOR CML UFAST 16-LFCSP RoHS:是 類別:集成電路 (IC) >> 線性 - 比較器 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:- 類型:通用 元件數(shù):1 輸出類型:CMOS,推挽式,滿擺幅,TTL 電壓 - 電源,單路/雙路(±):2.5 V ~ 5.5 V,±1.25 V ~ 2.75 V 電壓 - 輸入偏移(最小值):5mV @ 5.5V 電流 - 輸入偏壓(最小值):1pA @ 5.5V 電流 - 輸出(標(biāo)準(zhǔn)):- 電流 - 靜態(tài)(最大值):24µA CMRR, PSRR(標(biāo)準(zhǔn)):80dB CMRR,80dB PSRR 傳輸延遲(最大):450ns 磁滯:±3mV 工作溫度:-40°C ~ 85°C 封裝/外殼:6-WFBGA,CSPBGA 安裝類型:表面貼裝 包裝:管件 其它名稱:Q3554586 |

| ADCMP580BCPZ-WP | 功能描述:IC COMPARATOR CML UFAST 16-LFCSP RoHS:是 類別:集成電路 (IC) >> 線性 - 比較器 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 類型:通用 元件數(shù):1 輸出類型:CMOS,開路集電極,TTL 電壓 - 電源,單路/雙路(±):2.7 V ~ 5.5 V 電壓 - 輸入偏移(最小值):7mV @ 5V 電流 - 輸入偏壓(最小值):0.25µA @ 5V 電流 - 輸出(標(biāo)準(zhǔn)):84mA @ 5V 電流 - 靜態(tài)(最大值):120µA CMRR, PSRR(標(biāo)準(zhǔn)):- 傳輸延遲(最大):600ns 磁滯:- 工作溫度:-40°C ~ 85°C 封裝/外殼:SC-74A,SOT-753 安裝類型:表面貼裝 包裝:剪切帶 (CT) 產(chǎn)品目錄頁(yè)面:1268 (CN2011-ZH PDF) 其它名稱:*LMV331M5*LMV331M5/NOPBLMV331M5CT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。