- 您現在的位置:買賣IC網 > PDF目錄373982 > ADF4116BCP (ANALOG DEVICES INC) RF PLL Frequency Synthesizers PDF資料下載

參數資料

| 型號: | ADF4116BCP |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | XO, clock |

| 英文描述: | RF PLL Frequency Synthesizers |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 550 MHz, CQCC20 |

| 封裝: | CSP-20 |

| 文件頁數: | 10/20頁 |

| 文件大小: | 226K |

| 代理商: | ADF4116BCP |

ADF4116/ADF4117/ADF4118

–

10

–

REV. 0

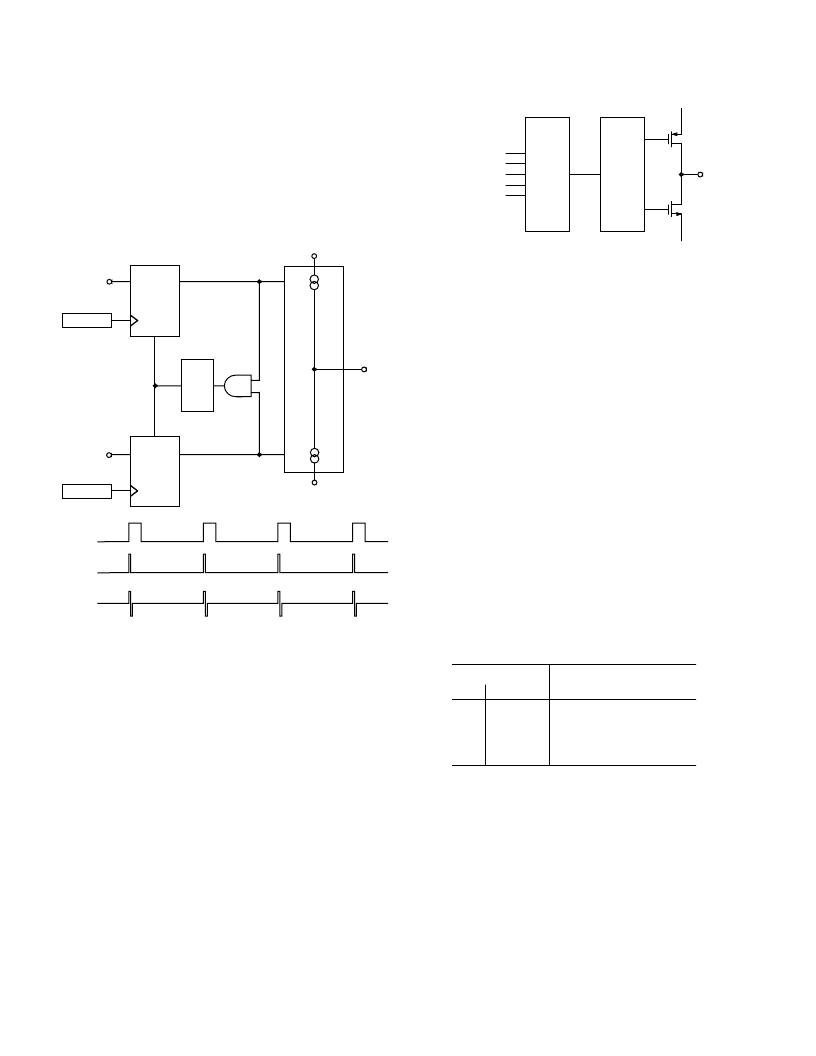

PHASE FREQUENCY DETECTOR (PFD) AND CHARGE

PUMP

The PFD takes inputs from the R counter and N counter and

produces an output proportional to the phase and frequency

difference between them. Figure 24 is a simplified schematic.

The PFD includes a fixed delay element which sets the width of

the antibacklash pulse. This is typically 3 ns. This pulse ensures

that there is no dead zone in the PFD transfer function and

gives a consistent reference spur level.

DELAY

U3

CLR1

Q1

D1

CP

DOWN

UP

HI

U1

CLR2

Q2

D2

U2

HI

N DIVIDER

R DIVIDER

V

P

CHARGE

PUMP

CP GND

R DIVIDER

CP OUTPUT

N DIVIDER

Figure 24. PFD Simpli

fi

ed Schematic and Timing (In Lock)

MUXOUT AND LOCK DETECT

The output multiplexer on the ADF4116 family allows the

user to access various internal points on the chip. The state of

MUXOUT is controlled by M3, M2 and M1 in the function

latch. Table VI shows the full truth table. Figure 25 shows the

MUXOUT section in block diagram form.

CONTROL

MUX

DV

DD

MUXOUT

DGND

ANALOG LOCK DETECT

DIGITAL LOCK DETECT

R COUNTER OUTPUT

N COUNTER OUTPUT

SDOUT

Figure 25. MUXOUT Circuit

Lock Detect

MUXOUT can be programmed for two types of lock detect:

Digital Lock Detect and Analog Lock Detect.

Digital Lock Detect is active high. It is set high when the phase

error on three consecutive phase detector cycles is less than 15 ns.

It will stay set high until a phase error of greater than 25 ns is

detected on any subsequent PD cycle.

The N-channel open-drain analog lock detect should be oper-

ated with an external pull-up resistor of 10 k

nominal. When

lock has been detected it is high with narrow low-going pulses.

INPUT SHIFT REGISTER

The ADF4116 family digital section includes a 21-bit input shift

register, a 14-bit R counter and a˙`-bit N counter, comprising

a 5-bit A counter and a 13-bit B counter. Data is clocked into

the 21-bit shift register on each rising edge of CLK. The data is

clocked in MSB first. Data is transferred from the shift register

to one of four latches on the rising edge of LE. The destination

latch is determined by the state of the two control bits (C2, C1)

in the shift register. These are the two LSBs DB1, DB0 as

shown in the timing diagram of Figure 1. The truth table for

these bits is shown in Table VII. Table II shows a summary

of how the latches are programmed.

Table II. C2, C1 Truth Table

Control Bits

C2

C1

Data Latch

0

0

1

1

0

1

0

1

R Counter

N Counter (A and B)

Function Latch

Initialization Latch

相關PDF資料 |

PDF描述 |

|---|---|

| ADF4116BRU | RF PLL Frequency Synthesizers |

| ADF4117 | RF PLL Frequency Synthesizers |

| ADF4153 | Fractional-N Frequency Synthesizer |

| ADF4153BCP | Fractional-N Frequency Synthesizer |

| ADF4153BCP-REEL | Fractional-N Frequency Synthesizer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADF4116BRU | 功能描述:IC SYNTH PLL RF 550MHZ 16-TSSOP RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:- 標準包裝:1,000 系列:Precision Edge® 類型:時鐘/頻率合成器 PLL:無 輸入:CML,PECL 輸出:CML 電路數:1 比率 - 輸入:輸出:2:1 差分 - 輸入:輸出:是/是 頻率 - 最大:10.7GHz 除法器/乘法器:無/無 電源電壓:2.375 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-VFQFN 裸露焊盤,16-MLF? 供應商設備封裝:16-MLF?(3x3) 包裝:帶卷 (TR) 其它名稱:SY58052UMGTRSY58052UMGTR-ND |

| ADF4116BRU-REEL | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 16-Pin TSSOP T/R 制造商:Analog Devices 功能描述:SINGLE INTEGER-N 550MHZ PLL |

| ADF4116BRU-REEL7 | 功能描述:IC PLL FREQ SYNTHESIZER 16-TSSOP RoHS:否 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:- 標準包裝:1,000 系列:Precision Edge® 類型:時鐘/頻率合成器 PLL:無 輸入:CML,PECL 輸出:CML 電路數:1 比率 - 輸入:輸出:2:1 差分 - 輸入:輸出:是/是 頻率 - 最大:10.7GHz 除法器/乘法器:無/無 電源電壓:2.375 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-VFQFN 裸露焊盤,16-MLF? 供應商設備封裝:16-MLF?(3x3) 包裝:帶卷 (TR) 其它名稱:SY58052UMGTRSY58052UMGTR-ND |

| ADF4116BRUZ | 功能描述:IC SYNTH PLL RF 550MHZ 16-TSSOP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發生器,PLL,頻率合成器 系列:- 標準包裝:2,000 系列:- 類型:PLL 頻率合成器 PLL:是 輸入:晶體 輸出:時鐘 電路數:1 比率 - 輸入:輸出:1:1 差分 - 輸入:輸出:無/無 頻率 - 最大:1GHz 除法器/乘法器:是/無 電源電壓:4.5 V ~ 5.5 V 工作溫度:-20°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-LSSOP(0.175",4.40mm 寬) 供應商設備封裝:16-SSOP 包裝:帶卷 (TR) 其它名稱:NJW1504V-TE1-NDNJW1504V-TE1TR |

| ADF4116BRUZ | 制造商:Analog Devices 功能描述:PLL, FREQUENCY SYNTHESIZER, 550MHZ, TSSO |

發布緊急采購,3分鐘左右您將得到回復。