- 您現在的位置:買賣IC網 > PDF目錄373982 > ADF4153 (Analog Devices, Inc.) Fractional-N Frequency Synthesizer PDF資料下載

參數資料

| 型號: | ADF4153 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Fractional-N Frequency Synthesizer |

| 中文描述: | 分數N頻率合成器 |

| 文件頁數: | 20/24頁 |

| 文件大小: | 354K |

| 代理商: | ADF4153 |

ADF4153

When enabled, it activates every time the user programs

Register R0 to set a new output frequency. However, if a cycle

slip occurs in the settling transient after the phase RESYNC

operation, the phase RESYNC is lost. This can be avoided by

delaying the RESYNC activation until the locking transient is

close to its final frequency. This is done by rewriting to R1 after

R1 has been set up as normal. Setting load control [DB23]

allows this. When set, instead of determining the fractional

denominator, the MOD bits [M12 to M1] are used to set a time

interval from when the new channel is programmed to the time

the RESYNC is activated. This is called the delay. Its value

should be programmed to set a time interval that is at least as

long as the RF PLL lock time.

Rev. A | Page 20 of 24

For example, if REF

IN

= 26 MHz and MOD = 130 to give

200 kHz output steps (f

RES

), and the RF loop has a settling

time of 150 μs, then delay should be programmed to 3,900,

as 26 MHz × 150 μs = 3,900.

If the application requires the delay to be greater than 4095, the

RESYNC bits should be increased. For example, if the lock time

above is 1.5 ms, the delay should be programmed to 26 MHz ×

1.5 ms = 39,000. In this case, program M12 to M1 to 3,900 and

program S4 to S1 to 10. The delay is 3,900 × 10 = 39,000.

SPURIOUS SIGNALS—PREDICTING WHERE THEY

WILL APPEAR

Just as in integer-N PLLs, spurs appear at PFD frequency offsets

from the carrier. In a fractional-N PLL, spurs also appear at

frequencies equal to the RF

OUT

channel step resolution (f

RES

).

The third-order fractional interpolator engine of the ADF4153

may also introduce subfractional spurs. If the fractional

denominator (MOD) is divisible by 2, spurs appear at 1/2 f

RES.

If

the fractional denominator (MOD) is divisible by 3, spurs

appear at 1/3 f

RES.

Harmonics of all spurs mentioned will also

appear. With the lowest spur mode enabled, the fractional and

subfractional spurs is attenuated dramatically. The worst-case

spurs appear when the fraction is programmed to (1/MOD).

For example, in a GSM 900 MHz system with a 26 MHz PFD

frequency and an RF

OUT

channel step resolution (f

RES

) of 200

kHz, the MOD = 130. PFD spurs appear at 26 MHz offset, and

fractional spurs appear at 200 kHz offset. Since MOD is

divisible by 2, subfractional spurs are also present at 100 kHz

offset.

FILTER DESIGN—ADISIMPLL

A filter design and analysis program is available to help the user

to implement PLL design. Visit

www.analog.com/pll

for a free

download of the ADIsimPLL software. The software designs,

simulates, and analyzes the entire PLL frequency domain and

time domain response. Various passive and active filter

architectures are allowed. REV. #2 of ADIsimPLL allows analysis

of the ADF4153.

INTERFACING

The ADF4153 has a simple SPI compatible serial interface for

writing to the device. SCLK, SDATA, and LE control the data

transfer. When LE (latch enable) is high, the 22 bits that have

been clocked into the input register on each rising edge of

the timing diagram and Table 5 for the latch truth table. The maximum allowable serial clock rate is 20 MHz. This

means that the maximum update rate possible for the device is

909 kHz or one update every 1.1 μs. This is more than adequate

for systems that have typical lock times in the hundreds of

microseconds.

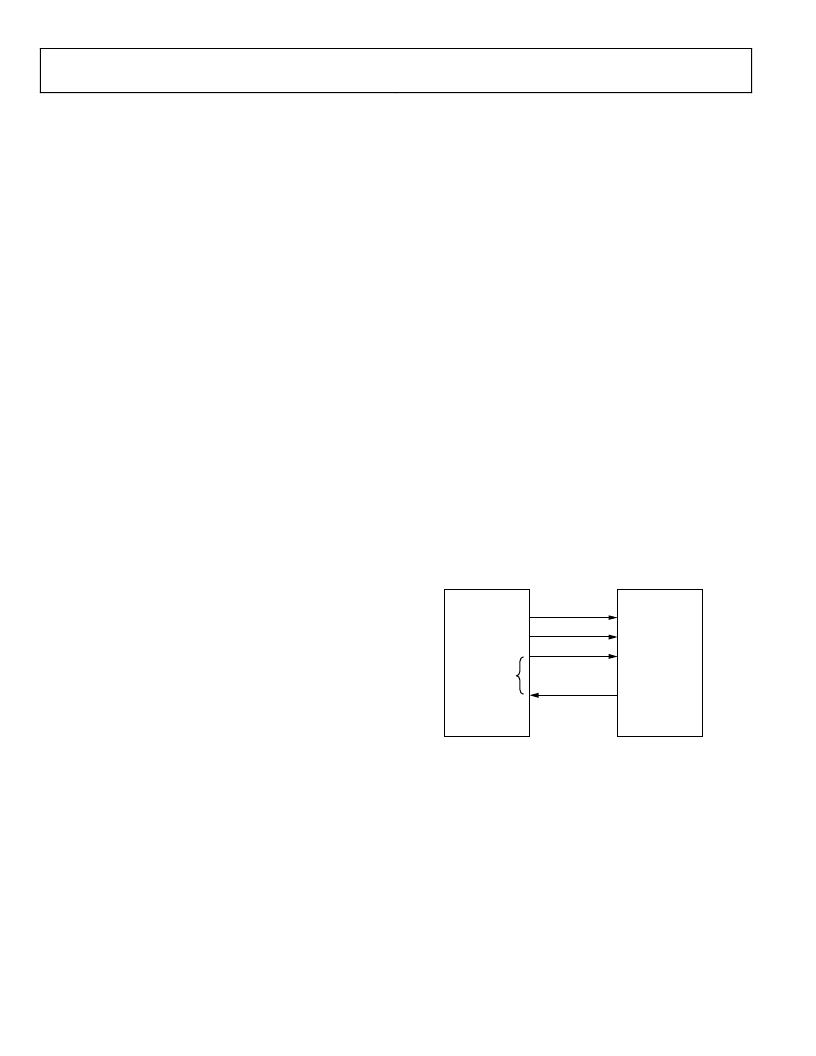

ADuC812 Interface

Figure 21 shows the interface between the ADF4153 and the

ADuC812 MicroConverter. Since the ADuC812 is based on an

8051 core, this interface can be used with any 8051-based

microcontroller. The MicroConverter is set up for SPI master

mode with CPHA = 0. To initiate the operation, the I/O port

driving LE is brought low. Each latch of the ADF4153 needs a

24-bit word, which is accomplished by writing three 8-bit bytes

from the MicroConverter to the device. After the third byte is

written, the LE input should be brought high to complete the

transfer.

When operating in the mode described, the maximum

SCLOCK rate of the ADuC812 is 4 MHz. This means that the

maximum rate at which the output frequency can be changed is

180 kHz.

ADuC812

ADF4153

SCLOCK

SCLK

SDATA

LE

MUXOUT

(LOCK DETECT)

MOSI

I/O PORTS

0

Figure 21. ADuC812 to ADF4153 Interface

相關PDF資料 |

PDF描述 |

|---|---|

| ADF4153BCP | Fractional-N Frequency Synthesizer |

| ADF4153BCP-REEL | Fractional-N Frequency Synthesizer |

| ADF4153BCP-REEL7 | Fractional-N Frequency Synthesizer |

| ADF4153BRU | Fractional-N Frequency Synthesizer |

| ADF4153BRU-REEL | Fractional-N Frequency Synthesizer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADF4153ABCPZ | 制造商:Analog Devices 功能描述:SINGLE RF F-N PLL 制造商:Analog Devices 功能描述:SINGLE RF F-N PLL - Trays 制造商:Analog Devices 功能描述:IC PLL FREQ SYNTHESIZER 20-LFCSP 制造商:Analog Devices 功能描述:IC FREQ SYNTHESIZER 4GHZ 20 制造商:Analog Devices 功能描述:IC, FREQ SYNTHESIZER, 4GHZ, 20LFCSP 制造商:Analog Devices Inc. 功能描述:Phase Locked Loops - PLL Single RF F-N PLL 制造商:Analog Devices 功能描述:PLL SYNTHESIZER, FREQUENCY, 4GHZ, LFCSP-20; PLL Type:Frequency Synthesis; Frequency:4GHz; Supply Current:20mA; Supply Voltage Min:2.7V; Supply Voltage Max:3.3V; Digital IC Case Style:LFCSP; No. of Pins:20; Package / Case:20-LFCSP 制造商:Analog Devices 功能描述:IC, FREQ SYNTHESIZER, 4GHZ, 20LFCSP; Synthesizer Type:Frequency; Frequency:4GHz; Supply Voltage Min:2.7V; Supply Voltage Max:3.3V; Supply Current:20mA; Digital IC Case Style:LFCSP; No. of Pins:20; Operating Temperature Min:-40C; ;RoHS Compliant: Yes 制造商:Analog Devices 功能描述:PLL SYNTHESIZER, FREQUENCY, 4GHZ, LFCSP-20; PLL Type:Frequency Synthesis; Frequency:4GHz; Supply Current:20mA; Supply Voltage Min:2.7V; Supply Voltage Max:3.3V; Digital IC Case Style:LFCSP; No. of Pins:20; Package / Case:20-LFCSP ;RoHS Compliant: Yes |

| ADF4153ABCPZ-RL7 | 制造商:Analog Devices 功能描述:SINGLE RF F-N PLL 制造商:Analog Devices 功能描述:Fractional-N Frequency Synthesizer 20-Pin LFCSP EP T/R 制造商:Analog Devices 功能描述:SINGLE RF F-N PLL - Tape and Reel 制造商:Analog Devices 功能描述:IC PLL FREQ SYNTHESIZER 20LFCSP 制造商:Analog Devices Inc. 功能描述:Phase Locked Loops - PLL Single RF F-N PLL |

| ADF4153ABRUZ | 制造商:Analog Devices 功能描述:SINGLE RF F-N PLL - Rail/Tube 制造商:Analog Devices 功能描述:ngle RF F-N PLL |

| ADF4153ABRUZ-RL7 | 制造商:Analog Devices 功能描述:SINGLE RF F-N PLL - Tape and Reel 制造商:Analog Devices 功能描述:Single RF F-N PLL |

| ADF4153BCP | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 20-Pin LFCSP EP 制造商:Analog Devices 功能描述:IC SYNTHESIZER PLL |

發布緊急采購,3分鐘左右您將得到回復。