- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373982 > ADF4154 (Analog Devices, Inc.) Fractional-N Frequency Synthesizer PDF資料下載

參數(shù)資料

| 型號(hào): | ADF4154 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | XO, clock |

| 英文描述: | Fractional-N Frequency Synthesizer |

| 中文描述: | 分?jǐn)?shù)N頻率合成器 |

| 文件頁數(shù): | 18/20頁 |

| 文件大小: | 470K |

| 代理商: | ADF4154 |

ADF4154

If fast-lock is not used, then use the following sequence:

Rev. 0 | Page 18 of 20

1.

Load the

noise and spur register

.

2.

Load the

control register

.

3.

Load the

R-divider register

with DB23 = 0 and other

necessary parameters.

4.

Load the

N-divider register

,

including fast-lock = 0

(DB23) for normal operation.

To change frequency, only Step 4 need be repeated.

FAST-LOCK: A WORKED EXAMPLE

Consider an example in which PLL has reference frequencies of

13 MHz and F

PFD

= 13 MHz and a required lock time of 50 μs.

Therefore, the PLL is set to wide bandwidth for 40 μs.

If the time period chosen for the wide bandwidth is 40 μs, then

Fast-lock timer value = time in wide bandwidth ×

F

PFD

Fast-lock timer value = 40 μs × 13 MHz = 520

Therefore, 520 has to be loaded into the R-divider register in

Step 1 of the sequence described in the Fast-Lock Timer and

Register Sequences section.

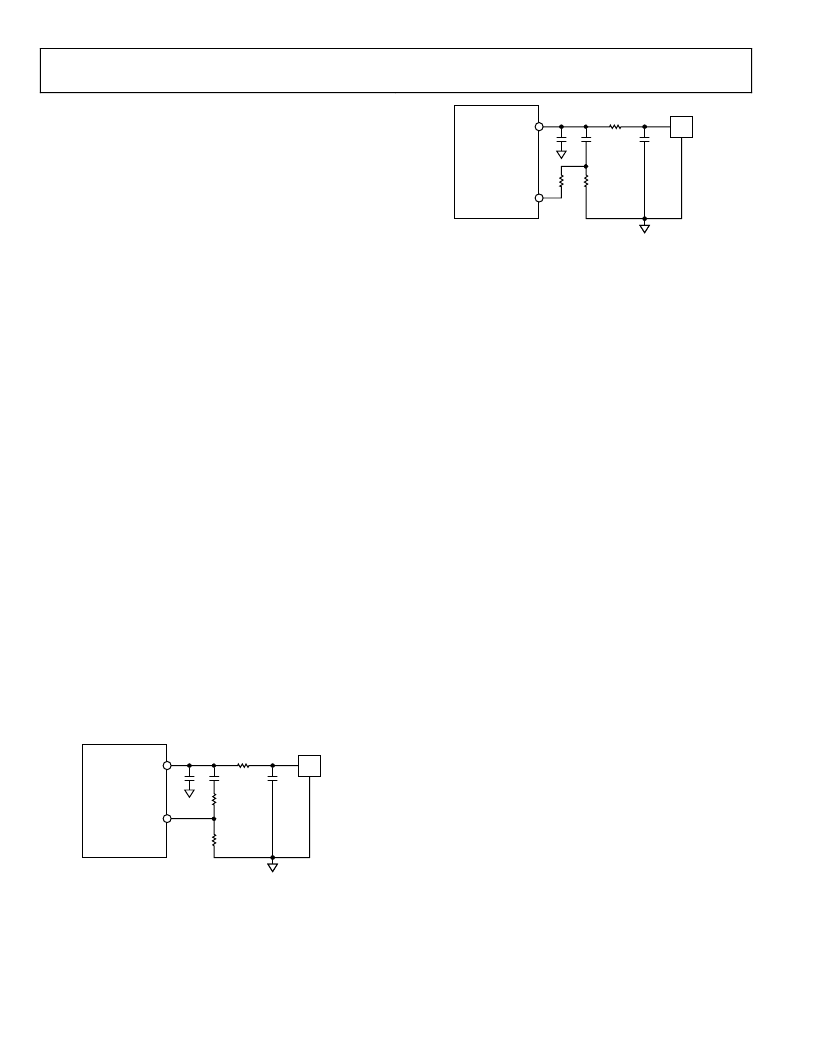

FAST-LOCK: LOOP FILTER TOPOLOGY

To use fast-lock mode, an extra connection from the PLL to the

loop filter is needed. The MUXOUT must reduce the damping

resistor in the loop filter to while in wide bandwidth mode.

This is required because the charge pump current is increased

by 16 while in wide bandwidth mode and stability must be

ensured. This can be done with the following two topologies:

1.

Divide the damping resistor (R1) into two values (R1 and

R1A) of ratio 1:3 (see Figure 22).

2.

Use an extra resistor (R1A) and connect it directly from the

MUXOUT, as shown in Figure 22. The extra resistor must

be chosen such that the parallel combination of an extra

resistor and the damping resistor (R1) is reduced to of

the original value of R1 alone (see Figure 23).

ADF4154

CP

MUXOUT

C1

C2

R2

R1

R1A

C3

VCO

0

Figure 22 Fast-lock Loop Filter Topology—Topology 1

ADF4154

CP

MUXOUT

C1

C2

R2

R1

R1A

C3

VCO

0

Figure 23. Fast-lock Loop Filter Topology—Topology 2

SPURIOUS SIGNALS

Predicting Where They Appear

As in integer-N PLLs, spurs appear at PFD frequency offsets

from the carrier. In a fractional-N PLL, spurs also appear at

frequencies equal to the RF

OUT

channel step resolution (f

RES

).

The third-order fractional interpolator engine of the ADF4154

may also introduce subfractional spurs. If the fractional deno-

minator (MOD) is divisible by 2, spurs appear at f

RES.

If the

fractional denominator (MOD) is divisible by 3, spurs appear at

1/3 f

RES.

Harmonics of all spurs mentioned also appear. With the

lowest spur mode enabled, the fractional and subfractional

spurs are attenuated dramatically. The worst-case spurs appear

when the fraction is programmed to 1/MOD. For example, in a

GSM 900 MHz system with a 26 MHz PFD frequency and an

RF

OUT

channel step resolution (f

RES

) of 200 kHz, the MOD = 130.

PFD spurs appear at 26 MHz offset and fractional spurs appear

at 200 kHz offset. Since the MOD is divisible by 2, subfractional

spurs are also present at 100 kHz offset.

FILTER DESIGN—ADISIMPLL

A filter design and analysis program is available to help the user

implement the PLL design. Visit www.analog.com/pll for a free

download of the ADIsimPLL software. The software designs,

simulates, and analyzes the entire PLL frequency and time

domain response. Various passive and active filter architectures

are allowed. Rev. 2 of ADIsimPLL allows analysis of the

ADF4154.

INTERFACING

The ADF4154 has a simple, SPI compatible serial interface for

writing to the device. SCLK, SDATA, and LE control the data

transfer. When LE (latch enable) is high, the 22 bits that have

been clocked into the input register on each rising edge of

SCLK are transferred to the appropriate latch. See Figure 2 for

the timing diagram and Table 5 for the latch truth table.

The maximum allowable serial clock rate is 20 MHz. This

means that the maximum update rate possible for the device is

909 kHz or one update every 1.1 μs. This is more than adequate

for systems that have typical lock times in the hundreds of

microseconds.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADF4154BCP | Fractional-N Frequency Synthesizer |

| ADF4154BCP-REEL | Fractional-N Frequency Synthesizer |

| ADF4154BCP-REEL7 | Fractional-N Frequency Synthesizer |

| ADF4154BRU | Fractional-N Frequency Synthesizer |

| ADF4154BRU-REEL | Fractional-N Frequency Synthesizer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADF4154BCP | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 20-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:FRACTIONAL-N SYNTH. W/FASTLOCK COUNTER - Bulk |

| ADF4154BCP-REEL | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 20-Pin LFCSP EP T/R 制造商:Rochester Electronics LLC 功能描述:FRACTIONAL-N SYNTH. W/FASTLOCK COUNTER - Tape and Reel |

| ADF4154BCP-REEL7 | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 20-Pin LFCSP EP T/R |

| ADF4154BCPZ | 功能描述:IC FRACTION-N FREQ SYNTH 20LFCSP RoHS:是 類別:集成電路 (IC) >> 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘發(fā)生器,PLL,頻率合成器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:Precision Edge® 類型:時(shí)鐘/頻率合成器 PLL:無 輸入:CML,PECL 輸出:CML 電路數(shù):1 比率 - 輸入:輸出:2:1 差分 - 輸入:輸出:是/是 頻率 - 最大:10.7GHz 除法器/乘法器:無/無 電源電壓:2.375 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-VFQFN 裸露焊盤,16-MLF? 供應(yīng)商設(shè)備封裝:16-MLF?(3x3) 包裝:帶卷 (TR) 其它名稱:SY58052UMGTRSY58052UMGTR-ND |

| ADF4154BCPZ-RL | 功能描述:IC FRACTION-N FREQ SYNTH 20LFCSP RoHS:是 類別:集成電路 (IC) >> 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘發(fā)生器,PLL,頻率合成器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:Precision Edge® 類型:時(shí)鐘/頻率合成器 PLL:無 輸入:CML,PECL 輸出:CML 電路數(shù):1 比率 - 輸入:輸出:2:1 差分 - 輸入:輸出:是/是 頻率 - 最大:10.7GHz 除法器/乘法器:無/無 電源電壓:2.375 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-VFQFN 裸露焊盤,16-MLF? 供應(yīng)商設(shè)備封裝:16-MLF?(3x3) 包裝:帶卷 (TR) 其它名稱:SY58052UMGTRSY58052UMGTR-ND |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。