- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373983 > ADF4360-3BCP (ANALOG DEVICES INC) Integrated Synthesizer and VCO PDF資料下載

參數(shù)資料

| 型號: | ADF4360-3BCP |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 無繩電話/電話 |

| 英文描述: | Integrated Synthesizer and VCO |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, QCC24 |

| 封裝: | 4 X 4 MM, MO-220-VGGD-2, LFCSP-24 |

| 文件頁數(shù): | 7/20頁 |

| 文件大小: | 336K |

| 代理商: | ADF4360-3BCP |

PRELIMINARY TECHNICAL DATA

ADF4360-2

REV. PrA 07/03

–7–

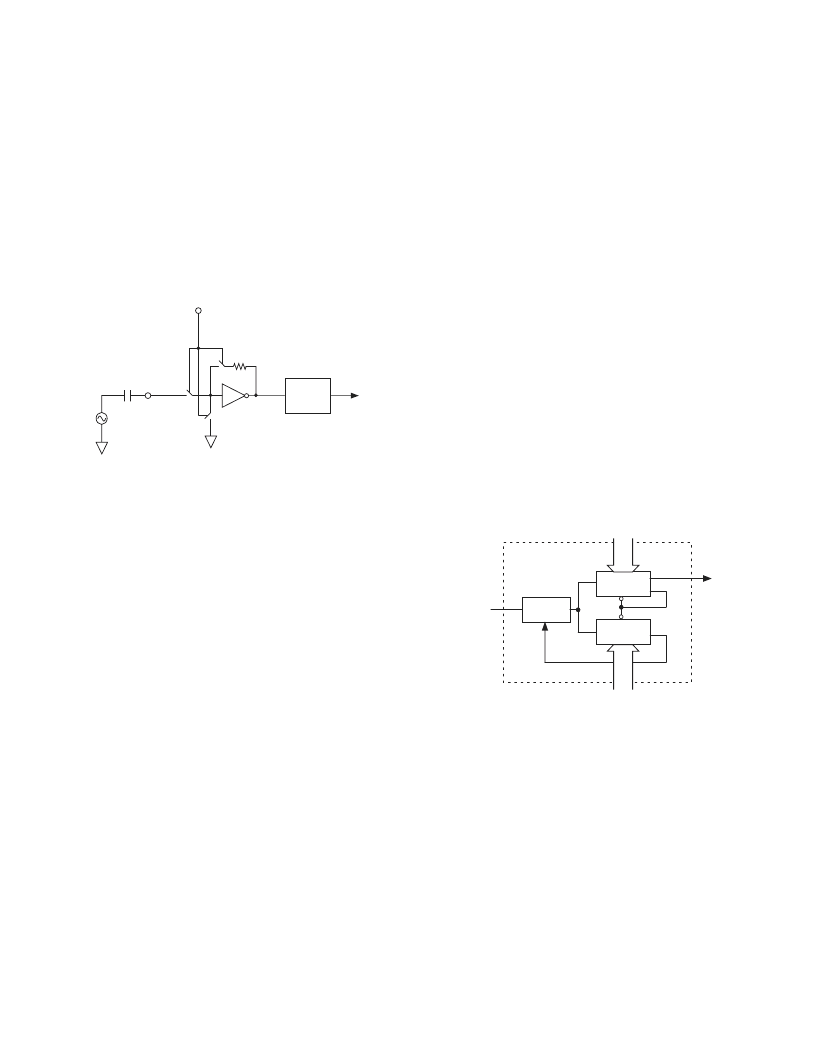

Figure 2. Reference Input Stage

A AND B COUNTERS

The A and B CMOS counters combine with the dual modulus

prescaler to allow a wide ranging division ratio in the PLL

feedback counter. The counters are specified to work when

the prescaler output is 300MHz or less. Thus, with an VCO

frequency of 2.5GHz, a prescaler value of 16/17 is valid but a

value of 8/9 is not valid.

Pulse Swallow Function

The A and B counters, in conjunction with the dual modulus

prescaler make it possible to generate output frequencies

which are spaced only by the Reference Frequency divided

by R . The equation for the VCO frequency is as follows:

f

VCO

= [(P x B) + A] x f

REFIN

/R

f

VCO

Ouput Frequency of voltage controlled oscillator

(VCO).

P

Preset modulus of dual modulus prescaler (8/9, 16/17,

etc.,).

B

Preset Divide Ratio of binary 13-bit counter (3 to

8191).

A

Preset Divide Ratio of binary 5-bit swallow

counter (0 to 31).

f

REFIN

External reference frequency oscillator.

Powerdown

Control

100k

NC

To R Counter

REF

IN

Buffer

NC

NO

SW1

SW2

SW3

CIRCUIT DESCRIPTION

REFERENCE INPUT SECTION

The Reference Input stage is shown below in Figure 2. SW1

and SW2 are normally-closed switches. SW3 is normally-

open. When Powerdown is initiated, SW3 is closed and SW1

and SW2 are opened. This ensures that there is no loading of

the REF

IN

pin on powerdown.

PRESCALER (P/P+1)

The dual modulus prescaler (P/P+1), along with the A and B

counters, enables the large division ratio, N, to be realised (N

= BP + A). The dual-modulus prescaler, operating at CML

levels, takes the clock from the VCO and divides it down to a

manageable frequency for the CMOS A and B counters. The

prescaler is programmable. It can be set in software to 8/9,

16/17 or 32/33. It is based on a synchronous 4/5 core. There

is a minimum divide ratio possible for fully contiguous output

frequencies. This minimum is determined by P, the prescaler

value and is given by: (P

2

-P).

Figure 3. A and B Counters

PRESCALER

P/P+1

13-BIT B

COUNTER

5-BIT A

COUNTER

LOAD

LOAD

N = BP + A

From VCO

To PFD

Modulus

Control

N DIVIDER

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADF4360-4BCP | Integrated Synthesizer and VCO |

| ADF4360-1BCP | Integrated Synthesizer and VCO |

| ADF4360-2 | Integrated Synthesizer and VCO |

| ADF4360-2BCP | Integrated Synthesizer and VCO |

| ADF4360-6BCP | Integrated Synthesizer and VCO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADF4360-3BCPRL | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 24-Pin LFCSP EP T/R |

| ADF4360-3BCPRL7 | 制造商:Analog Devices 功能描述:PLL Frequency Synthesizer Single 24-Pin LFCSP EP T/R |

| ADF4360-3BCPU1 | 制造商:Analog Devices 功能描述:PLL FREQ SYNTHESIZER SGL 24LFCSP EP - Bulk |

| ADF4360-3BCPZ | 功能描述:IC SYNTHESIZER VCO 24-LFCSP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 時鐘發(fā)生器,PLL,頻率合成器 系列:- 標(biāo)準(zhǔn)包裝:2,000 系列:- 類型:PLL 頻率合成器 PLL:是 輸入:晶體 輸出:時鐘 電路數(shù):1 比率 - 輸入:輸出:1:1 差分 - 輸入:輸出:無/無 頻率 - 最大:1GHz 除法器/乘法器:是/無 電源電壓:4.5 V ~ 5.5 V 工作溫度:-20°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-LSSOP(0.175",4.40mm 寬) 供應(yīng)商設(shè)備封裝:16-SSOP 包裝:帶卷 (TR) 其它名稱:NJW1504V-TE1-NDNJW1504V-TE1TR |

| ADF4360-3BCPZKL1 | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。